# Microprocesseur

Un processeur est défini par:

- ✓ Son architecture, c'est-à-dire son comportement vu par le programmeur, liée à:

- Son jeu d'instructions(en anglais Instruction Set Architecture, ISA);

- ➤ la largeur de ses registres internes de manipulation de données(8, 16, 32, 64, 128)bits et leur utilisation;

- les spécifications des entrées—sorties, de l'accès à la mémoire, etc.

3

# Microprocesseur

Un processeur est défini par:

- ✓ Ses caractéristiques, variables même entre processeurs compatibles,

- la cadence de son horloge exprimée en mégahertz (MHz) ou gigahertz (GHz);

- sa finesse de gravure exprimée en nanomètres (nm);

- son nombre de cœurs de calcul.

### **Architectures CISC/RISC**

Actuellement l'architecture des microprocesseurs se composent de deux grandes familles :

L'architecture CISC (Complex Instruction Set Computer)

Leurs instructions, de taille variable, sont variées et réalisent souvent des transferts avec la mémoire. Ces processeurs possèdent en général peu de registres, dont certains sont réservés pour des usages spécifiques.

Exemples: Intel 8086 et Motorola 68000 (pré-1985).

L'architecture RISC (Reduced Instruction Set Computer)

Leurs instructions, de taille fixe, sont régulières et peu d'entre elles

lisent ou écrivent en mémoire. Ces processeurs possèdent en

général de nombreux registres, lesquels sont uniformes.

Exemples: Alpha, Sparc, Mips, PowerPC (post-1985).

Le Pentium d'Intel mélange les deux designs...

| Architectures                                                                                                              | CISC/RISC:                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture RISC                                                                                                          | Architecture CISC                                                                                                                                                             |

| instructions simples ne prenant qu'un seul cycle instructions au format fixe décodeur simple (câblé) beaucoup de registres | <ul> <li>instructions complexes prenant plusieurs cycles</li> <li>instructions au format variable</li> <li>décodeur complexe (microcode)</li> <li>peu de registres</li> </ul> |

| <ul><li>peu de modes d'adressage</li><li>compilateur complexe</li></ul>                                                    | <ul><li>beaucoup de modes d'adressage</li><li>compilateur simple</li></ul>                                                                                                    |

|                                                                                                                            |                                                                                                                                                                               |

|                                                                                                                            | 6                                                                                                                                                                             |

### Mode Utilisateur/Superviseur:

Afin de mettre en oeuvre les mécanismes de protection nécessaires pour un système, le processeur possède deux modes de fonctionnement :

- Le mode superviseur: permet une plus grande sécurité pour le système. Quand le processeur est en mode superviseur, l'utilisateur ne peut pas accéder à certaines zones (ex: mémoire, registres...)

- Le mode utilisateur: Ce mode permet à l'utilisateur d'accéder uniquement aux zones réservées aux utilisateurs. Le processeur part en exception si l'utilisateur accède à une zone privilégiée.

Note: quand le processeur est en mode superviseur, le système peut accéder aux zone protégées et non protégées.

7

### Le microprocesseur MIPS R3000

- MIPS (de l'anglais Microprocessor without interlocked pipeline stages) a été développée par la compagnie MIPS Computer Systems Inc., basée en Californie.

- En 1988, la société MIPS Computer Systems, présente le MIPS R3000 qui succède au MIPS R2000.

- Son jeu d'instructions est de type RISC.

- Le processeur MIPS R3000 est un processeur 32 bits.

- •Le principal marché du MIPS: les applications embarquées, les ordinateurs de poche, les routeurs Cisco et les consoles de jeux vidéo (Nintendo 64 et Sony PlayStation, et PSP)...

- •Il existe plusieurs réalisations industrielles de cette architecture (Siemens, Toshiba, Philips, Silicon Graphics, etc...)

# Les registres

Les registres sont des zones de stockage temporaire située dans le processeur.

- La valeur de certains registres peut être lue ou modifiée par les instructions.

- Selon les modes de fonctionnement du processeur, il existe deux catégories de registres:

- Les registres non protégés (Accessibles en mode utilisateur)

- Les registres protégés (Accessibles en mode superviseur)

9

# Les registres généraux

- La machine MIPS dispose de 32 registres d'usage général de 32 bits chacun, dénotés \$0 à \$31.

- Les registres peuvent également être identités par un mnémonique indiquant leur usage conventionnel.

.0

# Les registres généraux

| Registre | Numéro | Usage Préservé par                          | l'appelé |

|----------|--------|---------------------------------------------|----------|

| zero     | 0      | Constante 0                                 |          |

| at       | 1      | Réservé pour l'assembleur                   | N        |

| v0       | 2      | Évaluation d'expressions et                 | N        |

| v1       | 3      | résultats d'une fonction                    | N        |

| a0-a3    | 4-7    | Arguments 1 à 4                             | N        |

| t0-t7    | 8-15   | Temporaires                                 | N        |

| s0-s7    | 16-23  | Temporaires sauvegardés                     | O        |

| t8       | 24     | Temporaire                                  | N        |

| t9       | 25     | Temporaire                                  | N        |

| k0       | 26     | Réservé pour le système d'exploitation      | N        |

| k1       | 27     | Réservé pour le système d'exploitation      | N        |

| gp       | 28     | Pointeur vers la zone des variables globale | O        |

| sp       | 29     | Pointeur de pile (stack pointer)            | O        |

| fp       | 30     | Pointeur de bloc (frame pointer)            | O        |

| ra       | 31     | Adresse de retour (pour les fonctions)      | O        |

|          |        |                                             |          |

|          |        |                                             |          |

# Les registres spéciaux

- -PC Registre compteur de programme (Program Counter), qui contient l'adresse mémoire de la prochaine instruction.

- -Hi et Lo : registres utilisés pour la multiplication et la division

- **SR** (status): Status Register :c'est le registre d'état. Il contient les masques d'interruption et le mode

- -CAUSE : contient la cause de l'interruption / exception

- **-EPC** : Exception PC (Program Counter) : adresse de l'instruction qui a causé l'exception

- BAR(vaddr): Bad Address Register ce registre contient l'adresse fautive en cas d'exception de type « adresse illégale »

### Format d'une instruction

Il y a 3 formats d'instructions différents :

- R: Register to Register Register Type

- I : Accès mémoire, branchements Immediate Type

- J: Instructions de sauts (non-conditionnels): Jump Type

13

### Format d'une instruction

- ➤ Le format R : est utilisé par les instructions nécessitant deux registres sources (RS et RT) et un registre résultat (RD).

- ➤ Le format I: est utilisé par les instructions de lecture/écriture mémoire, par les instructions utilisant un opérande immédiat, ainsi que par les branchements conditionnels.

- ➤ Le format J: n'est utilisé que pour les branchements inconditionnels.

|           | Forr  | nat d'un | e instru | ction |      |

|-----------|-------|----------|----------|-------|------|

| ➤ Le forr | nat R |          |          |       |      |

| Opcode    | Rs    | Rt       | Rd       | Sham  | Func |

| 6         | 5     | 5        | 5        | 5     | 6    |

| ➤ Le forr | nat I |          |          |       |      |

| Opcode    | Rs    | Rt       |          | Immed |      |

| 6         | 5     | 5        |          | 16    |      |

| ➤ Le forr | nat J |          |          |       |      |

| Opcode    |       |          | Immed    |       |      |

| 6         |       |          | 26       |       |      |

### Format d'une instruction

- ➢ le code binaire opcode (operation code) identifiant l'instruction Sur 6 bits, il ne permet de coder que 64 instructions, ce qui même pour un processeur RISC est peu. Par conséquent, un champ additionnel function de 6 bits est utilisé pour identifier les instructions Rtype.

- Rd est le registre destination (valeur sur 5 bits, donc comprise entre 0 et 31, codant le numéro du registre)

- Rs est le premier argument source

- > Rt est le second argument source

- ➤ Sham (shift amount) est le nombre de bits de décalage, pour les instructions de décalage.

- Func 6 bits additionnels pour le code des instructions R-type, en plus du champ opcode.

### pseudo-instruction

- pseudo-instruction ( macro-instruction) est une instruction qui ne fait pas partie du jeu d'instructions machine, mais qui est acceptée par l'assembleur qui la traduit en une séquence d'instructions machine.

- Les pseudo-instructions utilisent le registre \$1 si elles ont besoin de faire un calcul intermédiaire. Il faut donc éviter d'utiliser ce registre dans les programmes.

17

### pseudo-instruction

### **Pseudo-instruction move**

Comment traduire A=B?

- Sachant que A=\$t0, B=\$t1 et que le registre \$0 vaut toujours 0 on peut écrire :

- add \$t0, \$0, \$t1

- Il vaut mieux utiliser l'instruction move :

- move est une pseudo-instruction : sa traduction en langage machine

- est celle de add \$t0, \$0, \$t1.

# **Codage des instructions**

Le codage des instructions est principalement défini par les 6 bits du champ code opération de l'instruction (INS 31:26). Cependant, trois valeurs particulières de ce champ définissent en fait une famille d'instructions : il faut alors analyser d'autres bits de l'instruction pour décoder l'instruction. Ces codes particuliers sont :

- SPECIAL (valeur "000000"),

- BCOND (valeur "000001")

- COPRO (valeur "010000")

|     |         |       | DE   | CODAG | E OPCO | )   |      |      |

|-----|---------|-------|------|-------|--------|-----|------|------|

|     | 000     | 001   | 010  | 011   | 100    | 101 | 110  | 111  |

| 000 | SPECIAL | BCOND | J    | JAL   | BEQ    | BNE | BLEZ | BGTZ |

| 001 | ADDI    | ADDIU | SLTI | SLTIU | ANDI   | ORI | XORI | LUI  |

| 010 | COPRO   |       |      |       |        |     |      |      |

| 011 |         |       |      |       |        |     |      |      |

| 100 | LB      | LH    |      | LW    | LBU    | LHU |      |      |

| 101 | S8      | SH    |      | SW    |        |     |      |      |

| 110 |         |       |      |       |        |     |      |      |

| 111 |         |       |      |       |        |     |      |      |

|     |      |       |      | COD = S | nstruct |       |      |      |

|-----|------|-------|------|---------|---------|-------|------|------|

|     | 000  | 001   | 010  | 011     | 100     | 101   | 110  | 111  |

| 000 | SLL  |       | SRL  | SRA     | SLLV    |       | SRLV | SRAV |

| 001 | JR   | JALR  |      |         | SYSCALL | BREAK |      |      |

| 010 | MFHI | MTHI  | MFLO | MTLO    |         |       |      |      |

| 011 | MULT | MULTU | DIV  | DIVU    |         |       |      |      |

| 100 | ADD  | ADDU  | SUB  | SUBU    | AND     | OR    | XOR  | NOR  |

| 101 |      |       | SLT  | SLTU    |         |       |      |      |

| 110 |      |       |      |         |         |       |      |      |

| 111 |      |       |      |         |         |       |      |      |

|      |            |            | Couage ue        | s instructions      |      |

|------|------------|------------|------------------|---------------------|------|

|      |            |            |                  |                     |      |

| Te   | xt Segment |            |                  |                     |      |

| Bkpt | Address    | Code       | Basic            |                     | Sour |

|      | 0x00400000 | 0x3c011001 | lui \$1,4097     | 4: lw \$t1, x       |      |

|      |            |            | lw \$9,0(\$1)    |                     |      |

|      |            |            | addi \$1,\$0,1   | 5: subi \$t2,\$t1,1 |      |

|      |            |            | sub \$10,\$9,\$1 |                     |      |

|      |            |            | lui \$1,4097     | 6: sw \$t2, x       |      |

|      | 0x00400014 | 0xac2a0000 | sw \$10,0(\$1)   |                     |      |

|      |            |            |                  |                     |      |

|      |            |            |                  |                     |      |

|      |            |            |                  |                     |      |

|      |            |            |                  |                     |      |

|      |            |            |                  |                     |      |

|      |            |            |                  |                     |      |

|      |            |            |                  |                     |      |

| _    |            |            |                  |                     |      |

| Text Segment  Bkpt Address Code Basic Source  0x00400000 0x3c010001 lui \$1,1 4: lui \$1,1  0x00400004 0x24090005 addiu \$9,\$0,5 5: li \$t1,5  Text Segment  3kpt Address Code Basic Source  0x00400000 0x24090005 addiu \$9,\$0,5 4: li \$t1,5  0x00400000 0x24090005 addiu \$9,\$0,5 5 1i \$t2,6 |      |            |              | Codage            | d  | es                                      | instru        | ctic  | ns |        |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|--------------|-------------------|----|-----------------------------------------|---------------|-------|----|--------|--------|

| Bkpt   Address   Code   Basic   Source                                                                                                                                                                                                                                                              |      |            |              |                   |    |                                         |               |       |    |        |        |

| 0x00400000                                                                                                                                                                                                                                                                                          | Te   | xt Segment |              |                   |    |                                         |               |       |    |        |        |

| 0x00400004 0x24090005 addiu \$9,\$0,5   5: li \$t1,5                                                                                                                                                                                                                                                | Bkpt | Address    | Code         | Basic             | T  |                                         |               |       |    | Source |        |

| 0x00400004                                                                                                                                                                                                                                                                                          |      | 0x00400000 | 0x3c010001   | ui \$1,1          | 4: | lui 8                                   | 1,1           |       |    |        |        |

| Text Segment                                                                                                                                                                                                                                                                                        |      | 0x00400004 | 0x24090005 a | ddiu \$9.\$0.5    |    |                                         |               |       |    |        |        |

| 3kpt         Address         Code         Basic         Sour           0x00400000         0x24090005         addiu \$9,\$0,5         4: li \$t1,5           0x00400004         0x240a0006         addiu \$10,\$0,6         5: li \$t2,6                                                             |      |            |              |                   |    |                                         |               |       |    |        |        |

| Okpt         Address         Code         Basic         Sour           0x00400000         0x24090005         addiu \$9,\$0,5         4: li \$t1,5           0x00400004         0x240a0006         addiu \$10,\$0,6         5: li \$t2,6                                                             | Tou  | rt Coamont |              |                   |    |                                         |               |       |    |        |        |

| 0x00400000 0x24090005 addiu \$9,\$0,5 4: li \$t1,5                                                                                                                                                                                                                                                  | _    | - "        | Code         | Racin             |    | 100000000000000000000000000000000000000 |               |       |    |        | Source |

| 0x00400004 0x240a0006 addiu \$10,\$0,6 5: li \$t2,6                                                                                                                                                                                                                                                 | _    |            |              |                   |    | 4:                                      | li \$t1.5     |       |    |        | Ource  |

| 0-00100000 0-010-5000-33 411 40 410                                                                                                                                                                                                                                                                 | 1    |            |              |                   |    | _                                       |               |       |    |        |        |

| UXUU4UUUU8 UXU12a582U add \$11,\$9,\$10   0: add \$t3,\$t1,\$t2                                                                                                                                                                                                                                     |      | 0x00400008 | 0x012a5820   | add \$11,\$9,\$10 |    | 6:                                      | add \$t3,\$t1 | ,\$t2 |    |        |        |

|                                                                                                                                                                                                                                                                                                     |      |            |              |                   |    |                                         |               |       |    |        |        |

|                                                                                                                                                                                                                                                                                                     |      |            |              |                   |    |                                         |               |       |    |        |        |

|                                                                                                                                                                                                                                                                                                     |      |            |              |                   |    |                                         |               |       |    |        |        |

# **Codage des adresses**

- Les adresses dans les instructions ne sont pas sur 32 bits!

- ➤ Pour les instructions de type I : 16 bits

- > =) Adresse = PC + signé(16 bits) \* 4 adressage relatif

- ➤ Pour les instructions de type J : 26 bits

- =) On obtient l'adresse d'un mot mémoire (de 32 bits) en ajoutant devant les 26 bits les 4 bits de poids fort de PC (Il faut multiplier par 4 pour l'adresse d'un octet)

adressage direct restreint

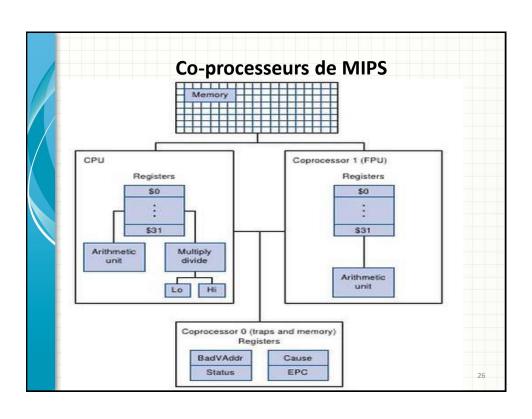

### Co-processeurs de MIPS

- Le microprocesseur Mips travaille avec des coprocesseurs pour effectuer des opérations spécifiques.

- ➤ Le co-processeur 0: (processeur de contrôle système) gère le système de mémoire virtuelle, les exceptions ainsi que les transitions entre les modes Superviseur et Utilisateur.

- Le co-processeur FPU: (Floating Point Unit) Est chargé d'effectuer les opérations arithmétiques à virgules flottantes.

Il possède 32 registres nommés: \$f0 - \$f31

# ORGANISATION DE LA MÉMOIRE EN MIPS R3000

# Mémoire et programme

- ➤ Quand on demande l'exécution d'un programme, celui-ci est chargé par le système d'exploitation (à partir du disque dur) dans une zone de la mémoire principale RAM.

- Chaque instruction est stockée dans une position mémoire.

- ▶ l'adresse (le numéro) de la case mémoire de début est transférée au processeur (placée dans le PC) pour qu'il commence l'exécution au bon endroit.

### Segmentation mémoire du MIPS R3000

- ➤ Dans l'architecture MIPS R3000, la mémoire est divisée en deux segments:

- Le segment utilisateur, et le segment noyau (mode superviseur).

- Quand le processeur est en mode superviseur, les 2 segments sont accessibles.

- Quand le processeur est en mode utilisateur, seul le segment utilisateur est accessible.

- Le processeur part en exception si une instruction essaie d'accéder à la mémoire avec une adresse correspondant au segment système alors que le processeur est en mode utilisateur.

29

### Segmentation mémoire du MIPS R3000

Un programme utilisateur utilise généralement trois sous segments (appelés sections) dans le segment utilisateur:

- •La section text contient le code exécutable en mode utilisateur.

- La section data contient les données globales manipulées par le programme utilisateur.

- •La section stack contient la pile d'exécution du programme utilisateur.

Trois sections sont également définies dans le segment noyau:

- •La section ktext contient le code exécutable en mode superviseur.

- •La section kdata contient les données globales manipulées par le système en mode superviseur.

- •La section kstack contient la pile d'exécution du noyau.

| Jog              |          | du MIPS R3000            | , |

|------------------|----------|--------------------------|---|

|                  | Reserved | 0xFFFFFFFF               |   |

|                  |          | 0xFFFFF000               |   |

|                  | .kstack  | 0xFFFFEFFF               |   |

|                  | Û        |                          |   |

| Segment<br>noyau | Î        |                          |   |

|                  | .kdata   |                          |   |

|                  |          | 0xC0000000               |   |

|                  |          | 0xBFFFFFF                |   |

|                  | .ktext   |                          |   |

|                  |          | 0x80000000               |   |

|                  | Reserved | 0x7FFFFFF                |   |

|                  | Reserved |                          |   |

|                  |          | 0x7FFFF000<br>0x7FFFEFFF |   |

|                  | .stack   | 0                        |   |

| Segment          | Û        |                          |   |

| utilisateur      | Û        |                          |   |

|                  | .data    |                          |   |

|                  |          | 0x10000000<br>0x0FFFFFF  |   |

|                  | .text    | UXUFFFFFF                |   |

|                  |          | 0x00400000               |   |

|                  |          | 0x00400000<br>0x003FFFFF |   |

## Adressage mémoire:

La mémoire est vue comme un tableau d'octets, qui contient aussi bien les données que les instructions.

- •L'unité d'adressage est l'octet.

- •Les instructions sont codées sur 32bits.

- Pour enregistrer une instruction quatre (4) octets sont nécessaires.

- •La représentation d'un mot(32-bits) en mémoire est comme suit:

# Adressage mémoire:

### Par exemple:

- num1: .word 42

- num2: .word 5.000.000

- 42<sub>10</sub> est représentée en hexadécimal par:0x0000002A

- 5,000,000<sub>10</sub> est représenté en hexadécimal par 0x004C4B40.

- La représentation de ces deux mots en mémoire est:

|   | Variables | Valeur | Adresses  |  |

|---|-----------|--------|-----------|--|

|   |           | ?      | 0x100100C |  |

|   |           | 00     | 0x100100B |  |

|   |           | 4C     | 0x100100A |  |

|   |           | 4B     | 0x1001009 |  |

|   | Num2 →    | 40     | 0x1001008 |  |

|   |           | 00     | 0x1001007 |  |

|   |           | 00     | 0x1001006 |  |

|   |           | 00     | 0x1001005 |  |

| 1 | Num1 →    | 2A     | 0x1001004 |  |

|   |           | ?      | 0x1001003 |  |