## Solution : SERIE T.D N°04 Sequential Circuits

#### Answers to course questions

**Q1:** In Sequential Logic Circuits, we have the presence of memory elements: A sequential logic circuit can be defined as a combinational circuit incorporating memory elements. It differs from combinational logic circuits in that its outputs depend not only on the inputs (combinational) but also on the state of its outputs.

Q2 : Here are examples of flip-flops (check the correct answers) :

☑ RS

☑ D

□ CLC

□ CLS

☑ JK

□ JSK

□ RAM

☑ T

**Q3 :** Two types of sequential logic circuits are distinguished :  $\Box$  Asynchronous  $\Box$  synchronous

Q4 : In an asynchronous logic circuit, a clock signal is used to coincide with the moments of writing

information into the flip-flops:  $\Box$  True  $\square$  False

Q5 : In a synchronous logic circuit, a clock signal is used to synchronize the moments of state change of the flip-flops :  $\square$  True  $\square$  False

Exercise 01 (solution is found at the end)

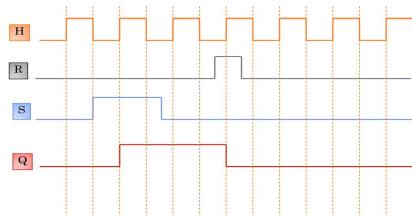

#### **Exercise 02 : (Solution)**

1- Simply perform a logical AND between its inputs and the clock signal, <u>to ensure that the</u> <u>consideration</u> of its inputs is synchronized with the clock signal.

Machine Structure -2, 2023/2024

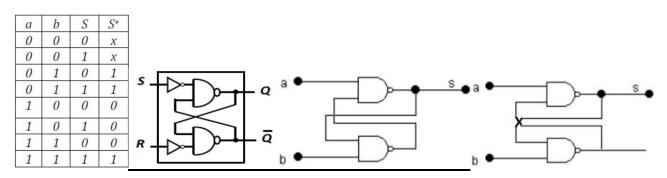

## **Exercise 03 : (Solution)**

1- The truth table:

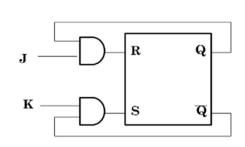

2- It is the Flip-flop SR with R = a and S = b.

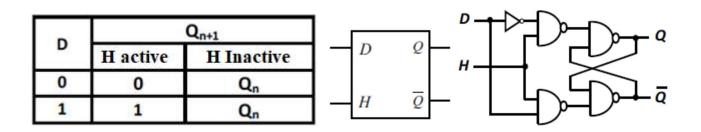

#### **Exercise 04 : (Solution)**

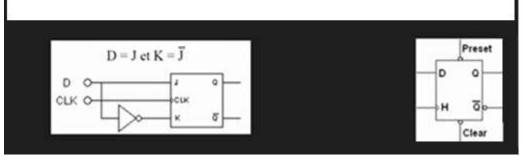

1- The D flip-flop is an RSH flip-flop where the R and S inputs are complemented to eliminate the forbidden state (R=S=1) and minimize the number of memory states.

- > When H is active and D=1, the output Q will be set to 1.

- > When H is active and D=0, the output Q will be reset to 0.

- > When H is not active, the outputs remain in the previous state (memory).

## Machine Structure -2, 2023/2024

| н | D | Q+ |

|---|---|----|

| 0 | 0 | Q- |

| 0 | 1 | Q- |

| 1 | 0 | 0  |

| 1 | 1 | 1  |

| н | R | S | $\mathbf{Q}$ +        |

|---|---|---|-----------------------|

| 0 | x | x | Q+<br><b>Q-</b><br>Q- |

| 1 | 0 | 0 | Q-                    |

| 1 | 0 | 1 | 1                     |

| 1 | 1 | 0 | 0                     |

| 1 | 1 | 1 | x                     |

$H_D = H_{RSH}, R = \overline{D}; S = D$

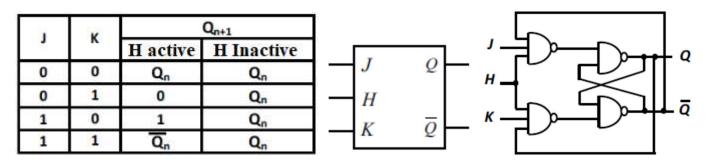

- 1- The JK flip-flop is an RSH flip-flop where the forbidden state (R=S=1) is eliminated by feedback looping the outputs to the inputs.

- 2- When H is active and J=1 and K=0, the output Q will be set to 1.

- 3- When H is active and J=0 and K=1, the output Q will be reset to 0.

- 4- When H is active and J=1 and K=1, the output Q will be toggled.

- 5- When H is not active or J=0 and K=0, the outputs remain in the previous state (memory).

|   | The truth table |   |   |                           |  |

|---|-----------------|---|---|---------------------------|--|

| н | J               | K | Q | Comment                   |  |

| 1 | 0               | 0 | 9 | Memory                    |  |

| 1 | 0               | 1 | 0 | Resetting the output Q    |  |

| 1 | 1               | 0 | 1 | Setting the output Q to 1 |  |

| 1 | 1               | 1 | ą | Toggling the output state |  |

1- The asynchronous JK flip-flop using an RS flip-flop.

| R | S | Q- | Q+ |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 0 | 1  | 1  |

| 0 | 1 | 0  | 1  |

| 0 | 1 | 1  | 1  |

| 1 | 0 | 0  | 0  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | 0  | X  |

| 1 | 1 | 1  | Х  |

| J | К | Q- | Q+ |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 0 | 1  | 1  |

| 0 | 1 | 0  | 1  |

| 0 | 1 | 1  | 1  |

| 1 | 0 | 0  | 0  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | 0  | 1  |

| 1 | 1 | 1  | 0  |

| x b b     |

|-----------|

| 5 T S R A |

| The truth table |   |   |   |                           |

|-----------------|---|---|---|---------------------------|

| н               | J | K | Q | Comment                   |

| 1               | 0 | 0 | 9 | Memory                    |

| 1               | 0 | 1 | 0 | Resetting the output Q    |

| 1               | 1 | 0 | 1 | Setting the output Q to 1 |

| 1               | 1 | 1 | ą | Toggling the output state |

## **Exercise 05 : (Solution)**

1-

| н   | D | Q+ |

|-----|---|----|

| 0/1 | 0 | Q- |

| 0/1 | 1 | Q- |

| ↑   | 0 | 0  |

| ↑   | 1 | 1  |

| н            | J | K | Q+ |

|--------------|---|---|----|

| 0/1          | Х | х | Q- |

| $\downarrow$ | 0 | 0 | Q- |

| $\downarrow$ | 0 | 1 | 0  |

| $\downarrow$ | 1 | 0 | 1  |

| $\downarrow$ | 1 | 1 | Q- |

$\mathbf{H}_{\mathrm{JK}} = \overline{\mathbf{H}}_{\mathrm{D}}, \, \mathbf{J} = \mathbf{D} \ ; \, \mathbf{K} = \overline{\mathbf{D}}$

The JK flip-flop avoids the situation R=S=1. It is used, notably, for counting. Another flip-flop that avoids R=S=1 is the D flip-flop. It can be constructed based on the RS or JK flip-flop.

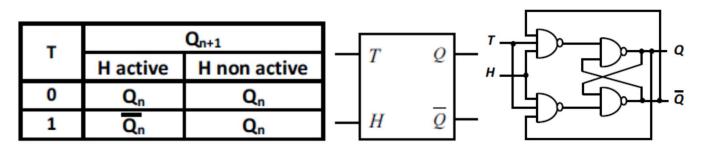

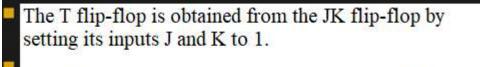

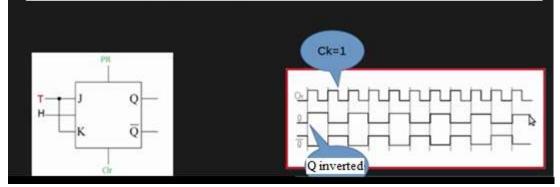

- 2- The T flip-flop is a flip-flop with a single input T. It is essentially a JK flip-flop with both inputs connected together

- > When H is active and T=1, the output Q will be toggled.

- > When H is not active or T=0, the outputs remain in the previous state (memory)

# **1** — The T flip-flop

Since J=K=1, the output of the flip-flop is toggled every time the clock is at 1.

| Т | Н            | Q+ |

|---|--------------|----|

| 0 | X            | Q- |

| 1 | 0/1,↑        | Q- |

| 1 | $\downarrow$ | Q- |

| н            | J | K | Q+ |

|--------------|---|---|----|

| 0/1,↑        | X | X | Q- |

| $\downarrow$ | 0 | 0 | Q- |

| $\downarrow$ | 0 | 1 | 0  |

| $\downarrow$ | 1 | 0 | 1  |

| $\downarrow$ | 1 | 1 | Q- |

$$H_T = H_{JK}, J = K = T$$

# Additional Exercises (Solution)

## **Exercise 06 : (Solution)**

| The D Flip-flop |   |   |   |

|-----------------|---|---|---|

| H               | D | Q | Q |

| t               | 0 | 0 | 1 |

| L               | 1 | 1 | 0 |

| The | JK | Fli | p-f | op |

|-----|----|-----|-----|----|

| _   |    | _   | r   |    |

| H | J | K | Q | Q |

|---|---|---|---|---|

| Ţ | 0 | 0 | q | q |

| J | 0 | 1 | 0 | 1 |

| Ţ | 1 | 0 | 1 | 0 |

| Ţ | 1 | 1 | q | q |

q = the value of Q just before the rising edge of the clock input.

## Exercise 07 (Solution) :

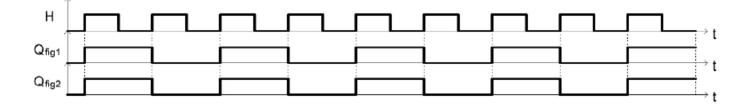

1- From the truth table of the AB flip-flop, we can define the values that the inputs J and K must have to provide the expected result: (Reminder of the truth table of the JK flip-flop).

| An | Bn | Q <sub>n+1</sub> | Jn | K |

|----|----|------------------|----|---|

| 0  | 0  | $\overline{Q}_n$ | 1  | 1 |

| 1  | 0  | Qn               | 0  | 0 |

| 0  | 1  | 1                | 1  | 0 |

| 1  | 1  | 0                | 0  | 1 |

|   | The truth table |   |                           |

|---|-----------------|---|---------------------------|

| J | K               | Q | Comment                   |

| 0 | 0               | 9 | Memory                    |

| 0 | 1               | 0 | Resetting the output Q    |

| 1 | 0               | 1 | Setting the output Q to 1 |

| 1 | 1               | ą | Toggling the output state |

The expressions of J and K are deduced based on A and B:

$$J = \overline{A}\overline{B} + \overline{A}B = \overline{A}$$

$$Q = \overline{A}\overline{B} + AB = \overline{A} \oplus \overline{B}$$

Hence, the logic diagram :

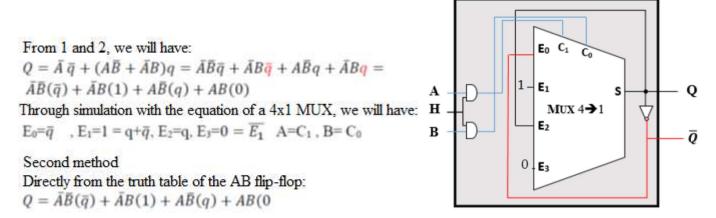

2- AB flip-flop based on a 4-to-1 MUX:

First method : From the question 1:

$J = \overline{A}\overline{B} + \overline{A}B = \overline{A}$  $Q = \overline{A}\overline{B} + AB = \overline{A} \oplus \overline{B}$ (1)

And according to the characteristic equation of the JK flip-flop:  $Q = I\overline{a} + \overline{K} a$  (2)

#### Exercise 01 (solution) :

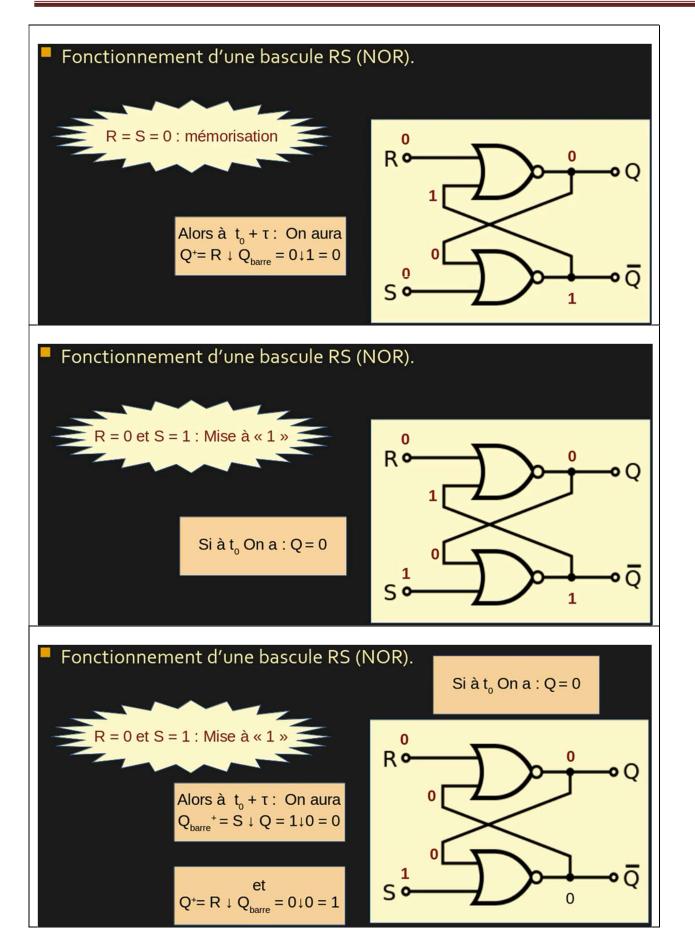

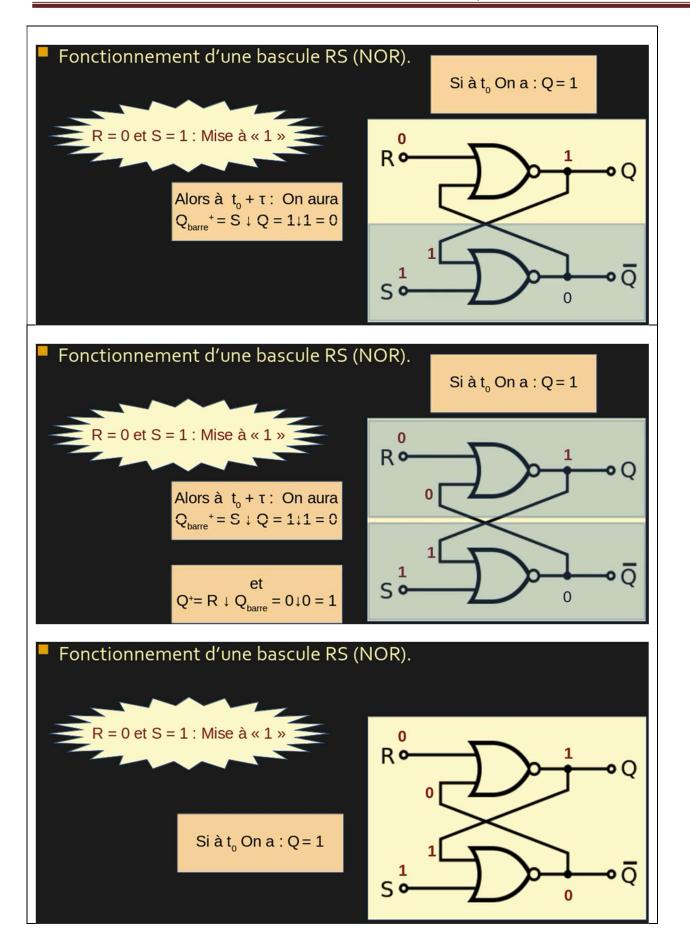

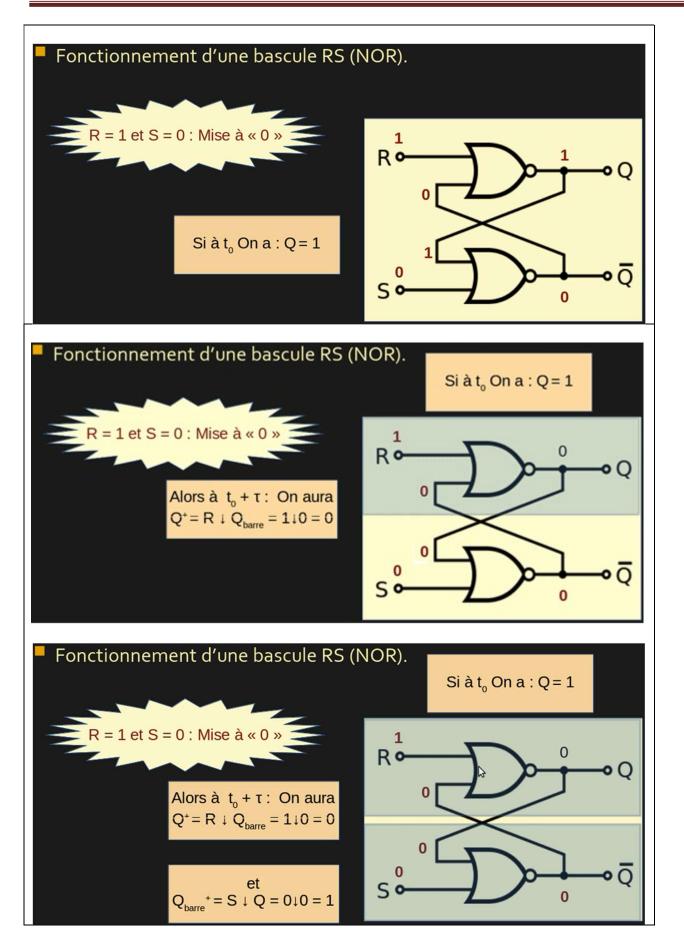

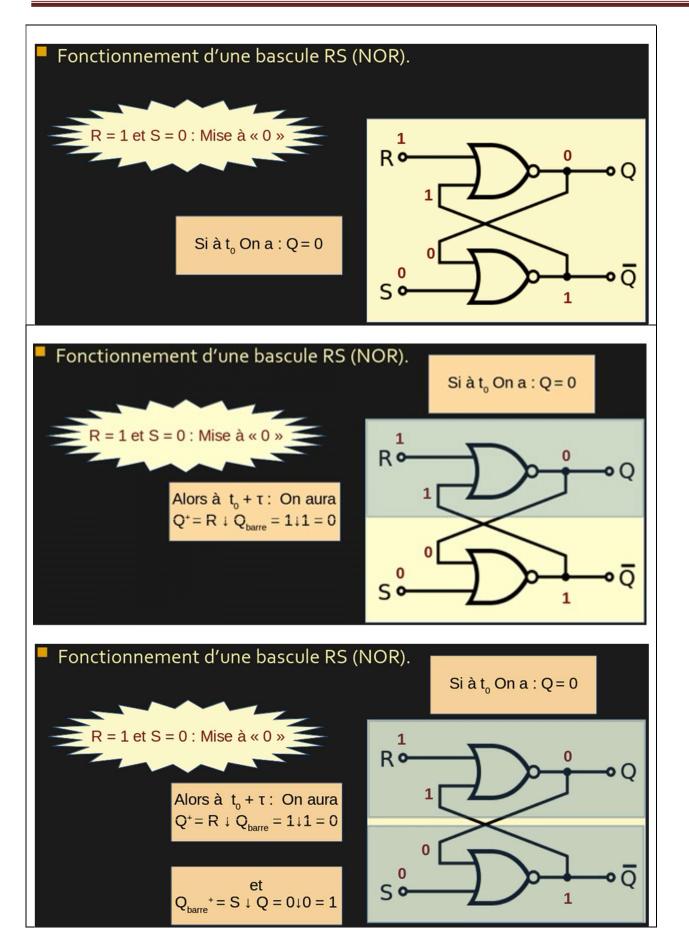

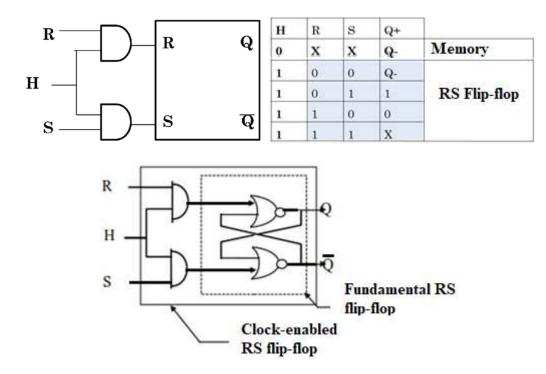

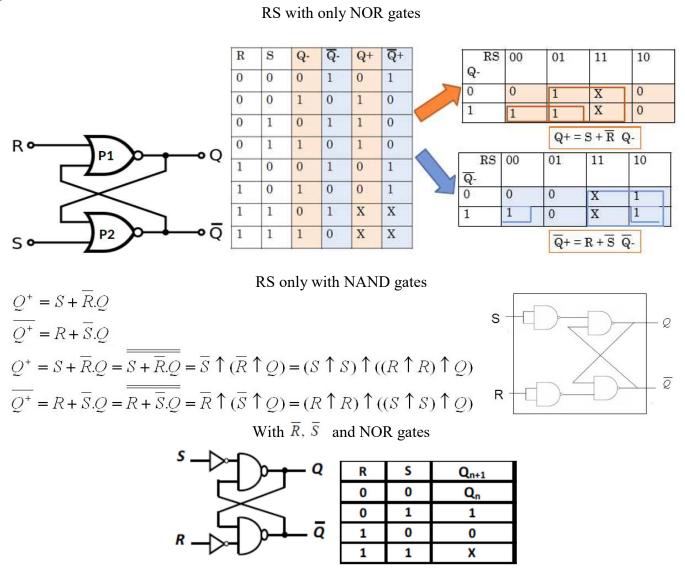

RS flip-flop (RS latch): The RS bistable (flip-flop) is a logic circuit capable, under certain circumstances, of maintaining the values of its outputs despite changes in input values, that is, of memorizing its state 'memory.' It is the storage element of sequential logic. It is controlled by two inputs, S and R, and has two outputs, Q and Q. The S input (Set) allows the output Q to be set to 1 (set), while R (Reset) allows it to be reset to 0 (clear). The most commonly encountered latches are implemented with two NOR or NAND gates.

The operation of an RS flip-flop (with NOR gates) R = S = 0: memory 0 R º 0 Si à  $t_0$  On a : Q = 1 0 S 0 The operation of an RS flip-flop (with NOR gates) R = S = 0: memory 0 R · 00 0 Alors à  $t_0 + \tau$ : On aura  $Q^{+}=R\downarrow \overset{\circ}{Q}_{\text{barre}}=0\downarrow 0=1$ O S The operation of an RS flip-flop (with NOR gates) R = S = 0: memory 0 R o 1 Si à  $t_0$  On a : Q = 0 ō 1

Analysis of RS Flip-flop Behavior using only NOR gates :

First year of computer science