## **Machine Structure 02**

# Chapter 04 The sequential circuits

## chapter plan

- 1. Introduction

- 2. Flip-flops

- 3. Counters

- 4. Registers

### **Introduction:**

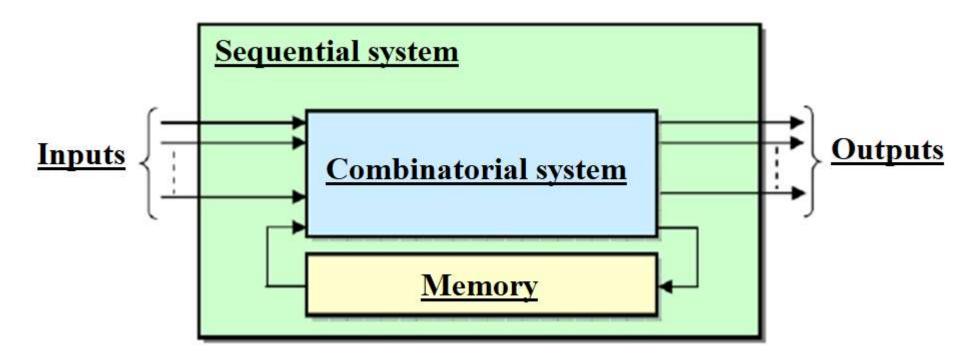

Several circuits used in everyday life need memory. Thus, A sequential system is a logical system whose state of the output variables depends on the state of the input variables + the previous state of the output variables.

The system remembers the past by recording the previous states of its outputs, calling for this, internal variables, or memories.

### **Introduction:**

(A sequential circuit is a digital (logic) circuit whose state at <u>time t+1</u> is a function of the inputs at the same <u>time t+1</u> and of the previous state of the system (<u>time t</u>).

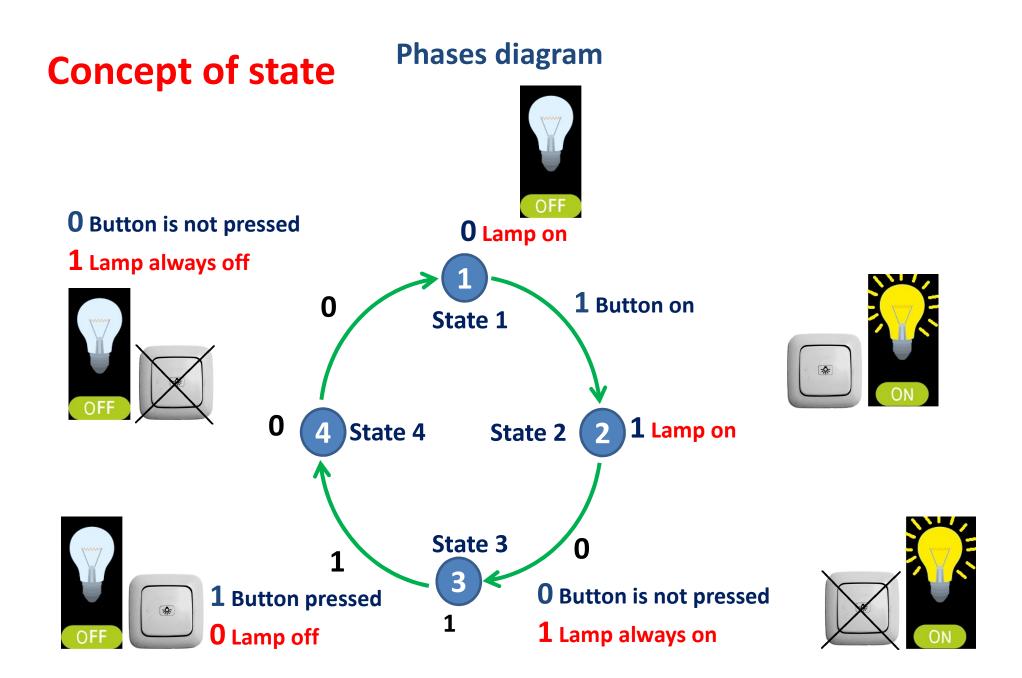

#### Concept of state:

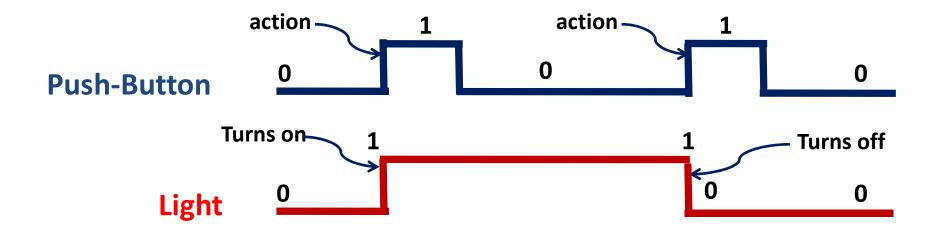

By way of illustration, let us take the example of an electric lamp controlled by a push button in such a way that an action on the button <u>turns on</u> the lamp, and that a successive action <u>turns it off</u>, according to the example of the following timing diagram :

#### **Concept of state**

The position (actuated or not), is not easily identifiable by the operator; an indicator light is often added to them, indicating the state of the circuit.

It should be noted that the evolution of the system depends not only on the position of the push button at a given moment, but also on whether the lamp is <u>on</u> or <u>not</u>.

**So:** The system therefore depends on the previous state because it retains the memory of the previous action; this is the **essential** characteristic of a sequential system.

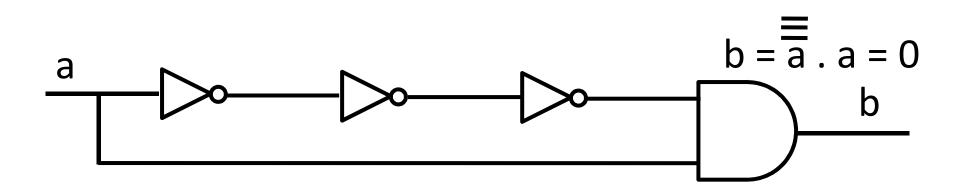

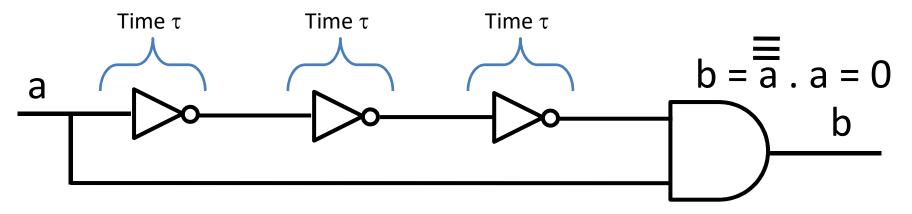

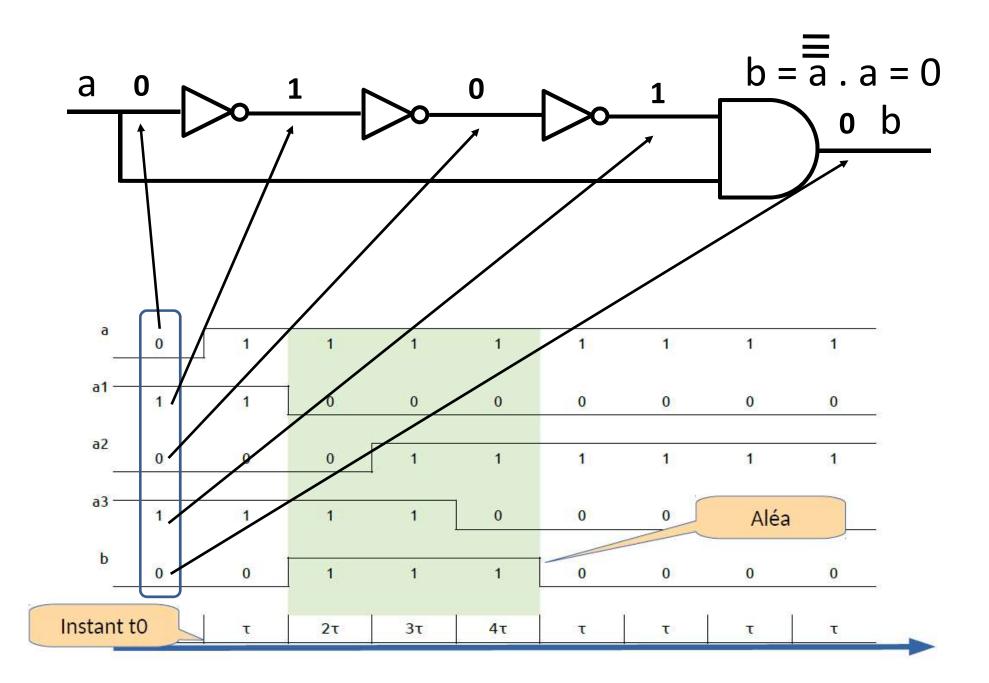

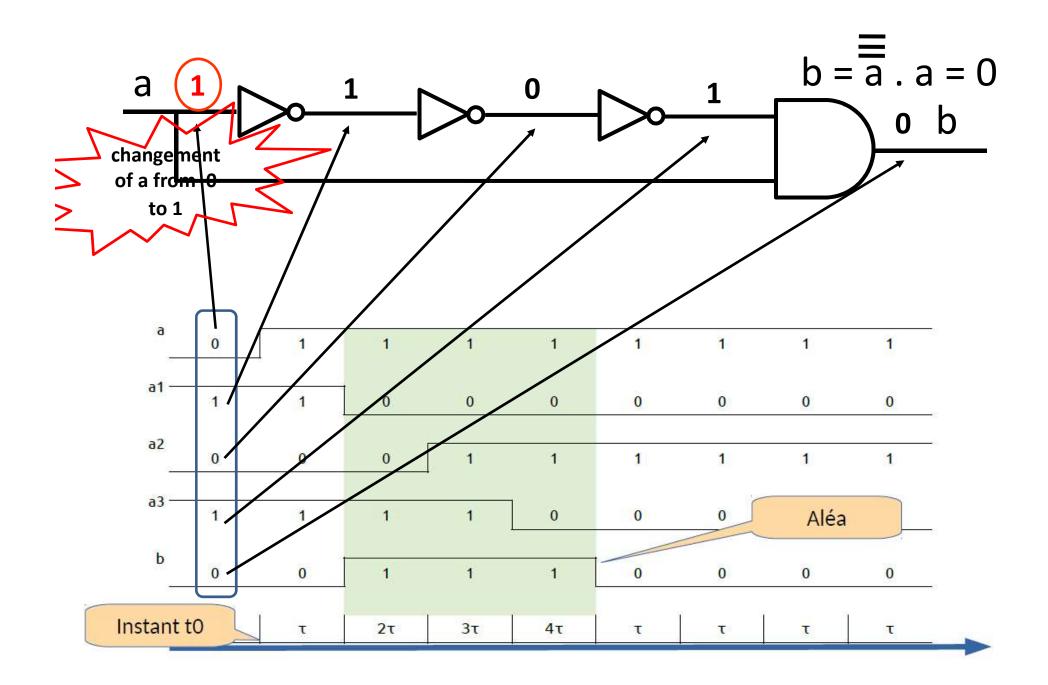

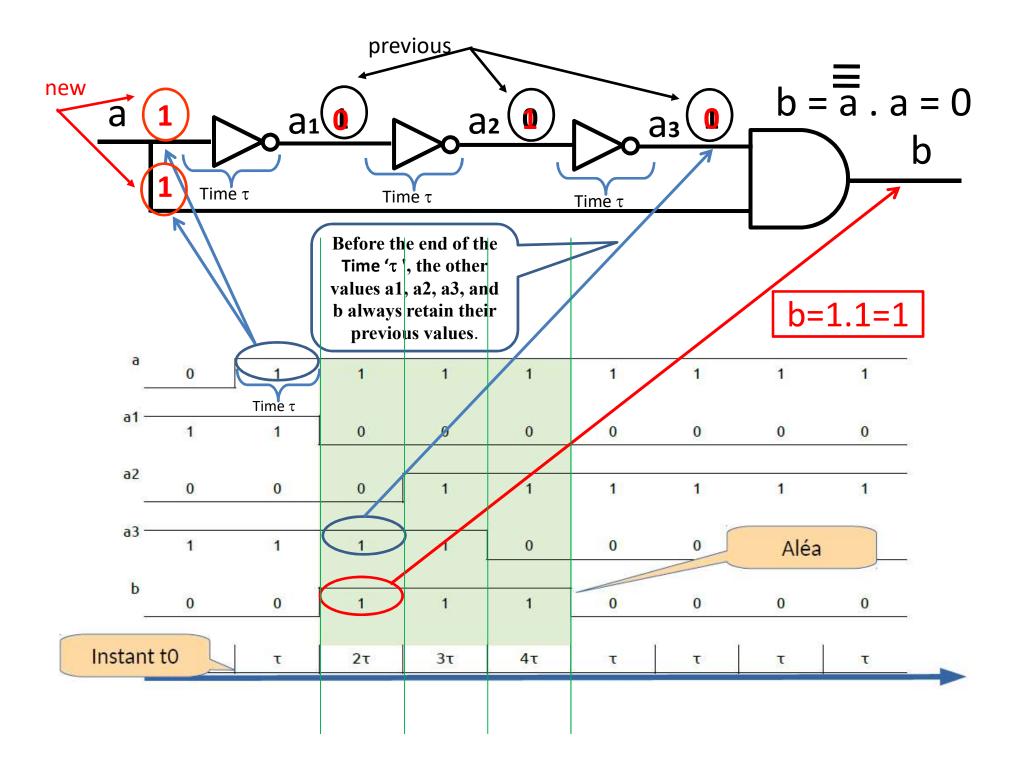

#### **Signal propagation delay :**

The design of sequential logic circuits takes into account a property that we ignored in combinatorial circuits. This is the propagation delay of the electrical signals through the logic gates. Example :

#### **Signal propagation delay :**

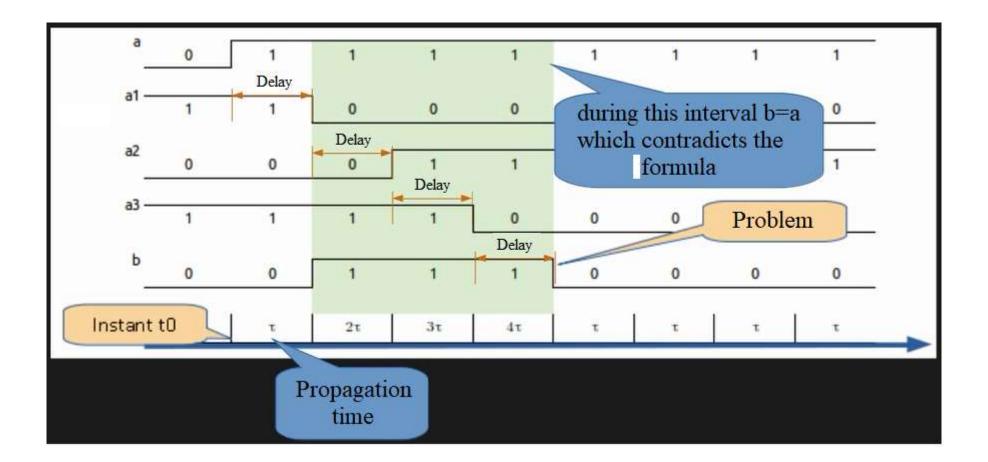

Indeed, we assumed that as soon as a change occurs in the inputs of a combinatorial circuit, immediately the outputs are affected. In reality, each logic gate will always take a certain time (called propagation time = Time  $\tau$ ) to pass an electrical signal from its input to its output.

In principle, based on the combinatorial logic circuits, the output of this circuit should always be equal to 0.

You will see, in reality that there is a small randomness (problem) that occurs when we change the value of the input "a".

Suppose that each of the gates (here "NOT" and "AND") takes a time equal to  $\tau$ .

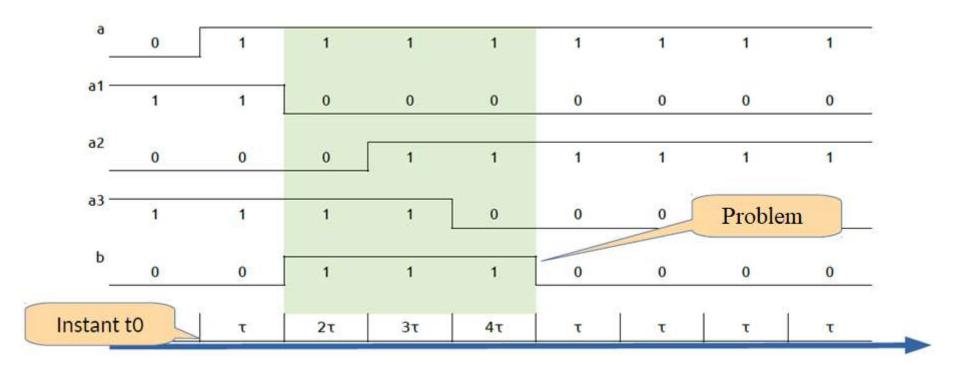

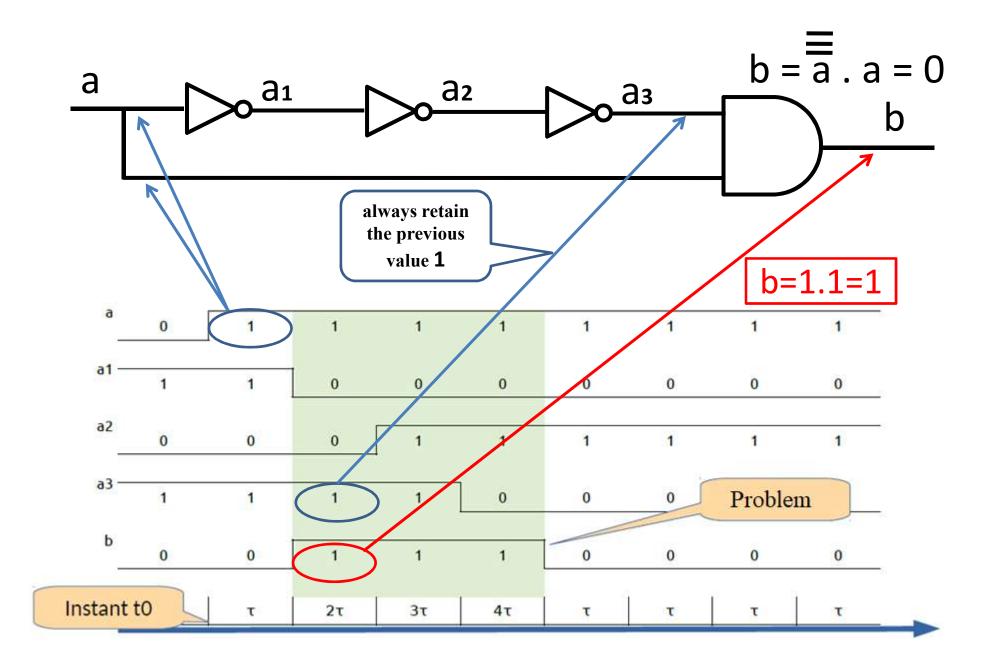

Let's plot in a temporal graph (which we call chronogram) the evolution of our signals: (a, a1, a2, a3 and b)

(a, a1, a2, a3 and b).

Note: The time diagram indicated below is called "chronogram". It is often used to show the functions of sequential logic circuits.

Let's assume that the value of 'a' switches from: '0' to '1' at time to.

• At time  $(t_0+\tau)$ , 'a1' reverts to 0 (thus 'a1' is the inverse of 'a').

- At time (t0+2τ), 'a2' transitions to 1 (then 'a2' is the inverse of 'a1').

- At time (to+3τ), 'as' transitions to 0 (then 'as' is the inverse of 'az').

- It should be noted that between (to) and (to+3τ), 'a' and 'as' are both at '1'

- simultaneously, which creates a particular situation for 'b' being equal to '1'.

#### Types of sequential circuits:

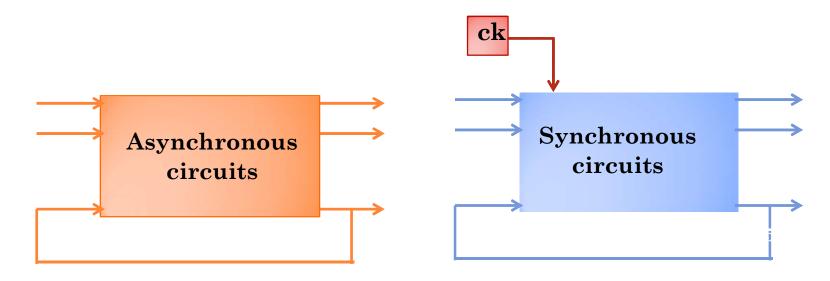

There are two types of sequential circuits:

Synchronous: where the behavior is determined by signals at discrete moments (measured, moderated) of time (clocked at the rhythm of a signal called 'clock' or CLK);

Asynchronous: where the behavior is determined by signals at any moment, and the order in which inputs change. Thus, in:

Asynchronous circuits: the output is modified as soon as there is a change in the <u>state of the inputs</u>.

In synchronous circuits: the output changes only after a <u>clock signal</u>.

Synchronous System (Concept of Clock)

Synchronization is achieved using a <u>clock</u>, which provides a periodic signal.

This periodic signal is distributed throughout the system so that storage elements are only affected with the arrival of a clock pulse.

The clock determines <u>when</u> there is activity in the circuit, and the other signals determine <u>what</u> (i.e., what changes) in the circuit.

The storage elements controlled by the clock transition are called flip-flops

- The flip-flop is the basic element allowing the construction of sequential circuits (Memory, Register, Counter, etc.).

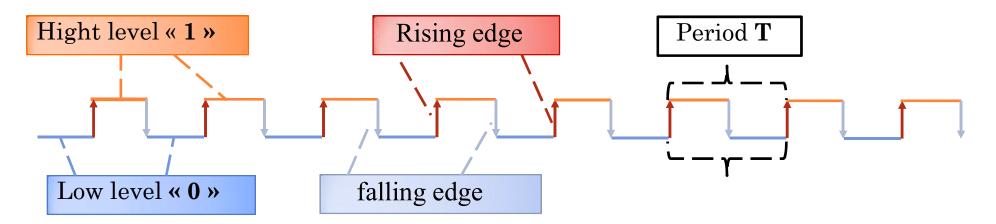

- A clock is a logical variable that successively transitions from <u>0 to 1</u> and from <u>1 to 0</u> periodically.

- This variable is often used as an input in sequential circuits (the clock is denoted by <u>**h**</u> or <u>**ck**</u> (clock)).

- Introduction to Sequential Circuits:

- Combinational Circuits: Output functions are expressed based on logical expressions of only the input variables.

- Sequential Circuits: Output functions depend not only on the current state of the input variables but also on the previous (past) state of certain output variables (memory properties).

#### **The concept of Clock**

A clock, noted by  $\underline{\mathbf{H}}$  or  $\underline{\mathbf{ck}}$  (clock), is a logical variable that successively transitions from  $\underline{\mathbf{0} \text{ to } \mathbf{1}}$  and from  $\underline{\mathbf{1} \text{ to } \mathbf{0}}$  periodically:

Frequency = 1/T = number of changes per second in hertz Hz

| Clock     | Period         |

|-----------|----------------|

| 1 Hz      | 1 second       |

| 1 Mega Hz | 1 milli-second |

| 1 Giga Hz | 1 nano-second  |

#### Introduction

Asynchronous Circuits: System variables <u>evolve</u> <u>freely</u> over time.

Synchronous Circuits: The evolution of variables depends on a <u>clock pulse</u> as one of the input signals.

## **Part1: Flip-Flops**

#### **Flip-Flops**

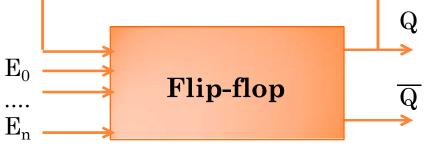

A flip-flop is a logical circuit capable, under certain circumstances, of maintaining the values of its outputs despite changes in input values, that is, of memorizing its state or 'memory.' It is the memory element of sequential logic.

Two main categories of flip-flops are distinguished:

- Asynchronous flip-flops, also called latches

- Synchronous flip-flops (dependent on a clock signal), simply called flip-flops.

#### Flip-flop:

#### A Flip-Flop:

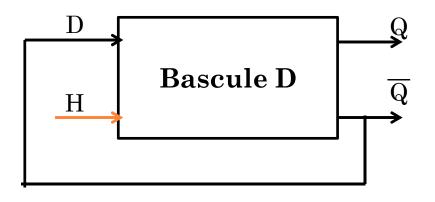

A flip-flop is a basic sequential circuit element that allows for the storage of a binary (bit) information. It can be synchronous or asynchronous and has two complementary outputs, Q and  $\overline{Q}$ .  $Q_{-} = Q(t)$

Examples include: RS flip-flop D flip-flop JK flip-flop T flip-flop, etc.

$$Q+ = Q (t+1) = F (Ei, Q-)$$

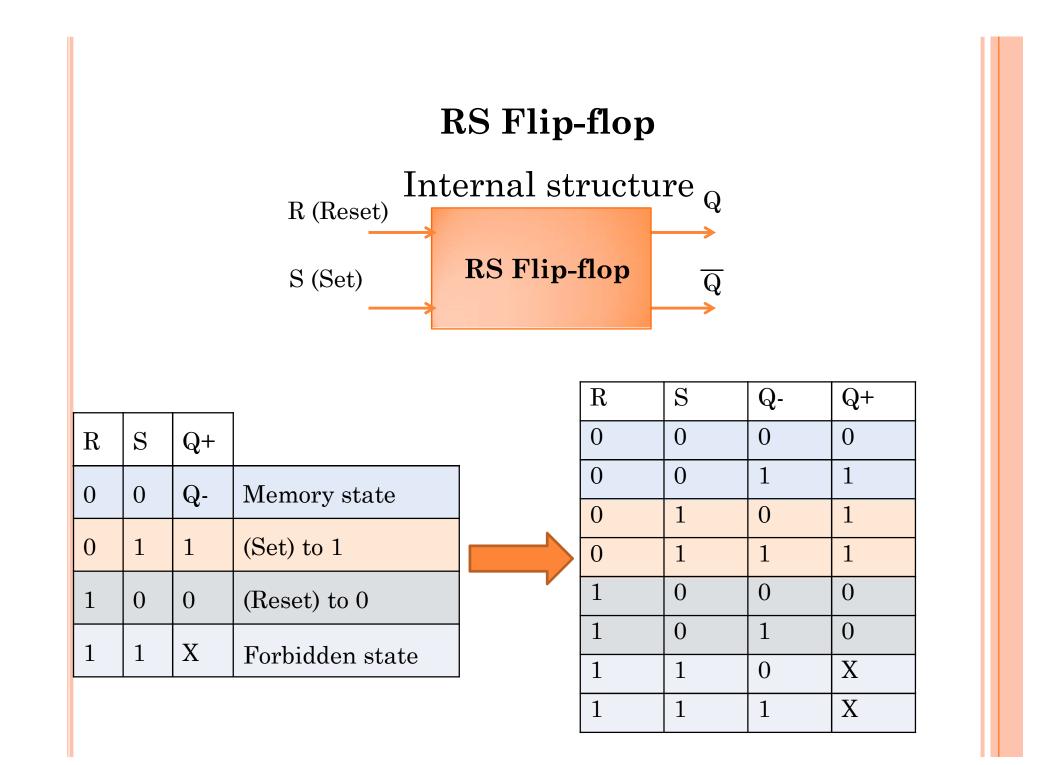

## **BASCULE RS**

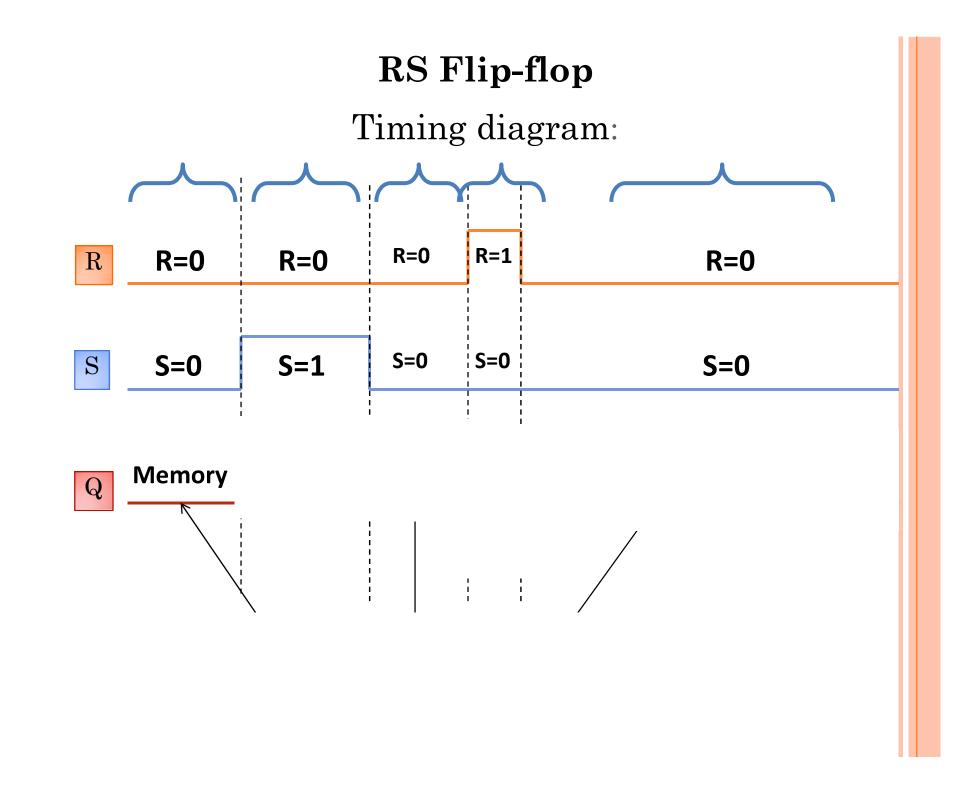

| R | S | Q+ |                   |

|---|---|----|-------------------|

| 0 | 0 | Q- | Memory State      |

| 0 | 1 | 1  | Set to 1          |

| 1 | 0 | 0  | Reset to 0        |

| 1 | 1 | X  | Not allowed State |

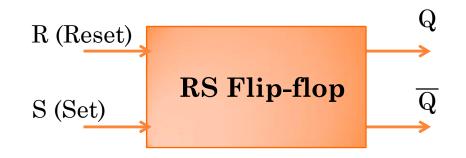

#### **RS Flip-Flop Definition:**

In the name of this flip-flop, you notice two letters: 'R' and 'S'.

These are the inputs of this flip-flop:

✓ 'R' for reset or setting to zero '0' and

✓ 'S' for set or setting to one '1'.

Of course, this flip-flop will have an output that we will call Q. In reality, we will always have two outputs: Q and Q-bar: Q and  $\overline{Q}$ .

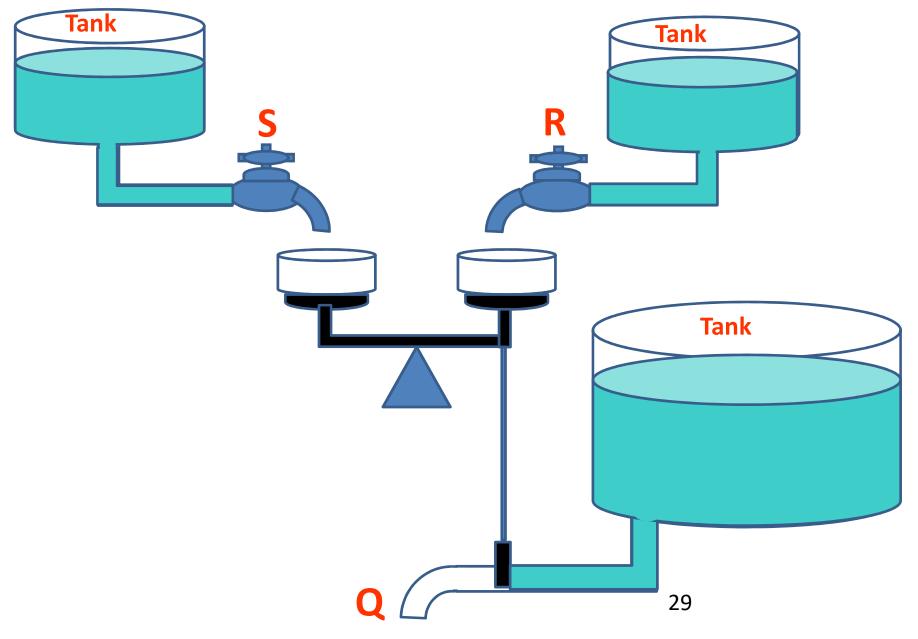

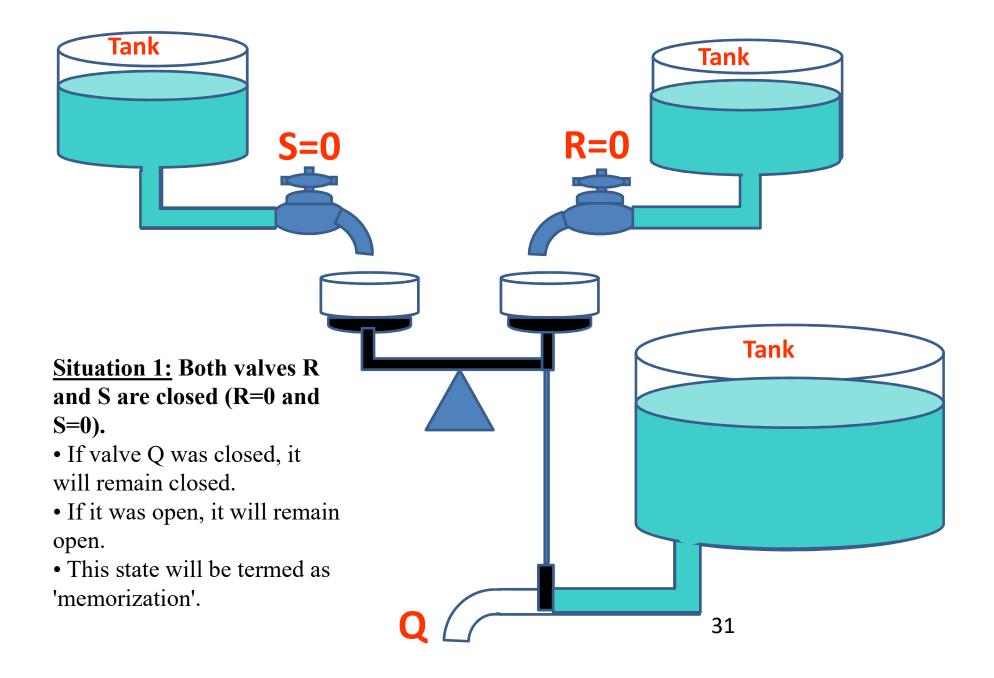

#### Example of RS Flip-Flop Operation:

#### **Example of RS Flip-Flop Operation:**

- Two valves R and S

- One flip-flop

- One output Q, which is a pipe

- R = 1 means that valve R is open (same for S)

- R = 0 means that valve R is closed (same for S)

- Output Q (output pipe) at '1' means water is being discharged

- Output Q (output pipe) at '0' means water is not being discharged

- The right part of the flip-flop is connected to a rod that operates a valve to open or close the output pipe Q.

Tank Tank S=1 **R=0** Tank Situation 2: I open valve 'S' while keeping valve 'R' closed (so S=1 and R=0): The flip-flop tilts to the left, lifting valve Q, allowing water to flow out. Therefore, we have Q=1. We will say that we have set our flip-flop to '1'. **Q=**1 32

Tank Tank **S=0 R=0** Tank Situation 3: I close valve 'S', knowing that valve 'R' is already closed (so S=0 and **R=0):** the flip-flop remains tilted to the left, lifting valve Q, allowing water to flow out. Therefore, we have Q=1. We will say that we have memorized the previous state (here, the state '1') of our flip-Q=133 flop.

Situation 4: I open valve 'R', knowing that valve 'S' is already closed (so S=0 and R=1): the flip-flop will tilt to the right, closing valve Q, stopping the flow of water out. Therefore, we have Q=0. We will say that we have reset the flip-flop (no water output). Q=0

**S=0**

Tank

Tank **R=1** Tank

34

Tank Tank **S=0 R=0** Tank Situation 5: I close valve 'R', knowing that valve 'S' is already closed (so S=0 and **R=0):** the flip-flop remains tilted to the right, closing valve Q, stopping the flow of water out. Therefore, we have Q=0. We will say that we have memorized the previous state (here, the state '0') of our flip- Q=035 flop.

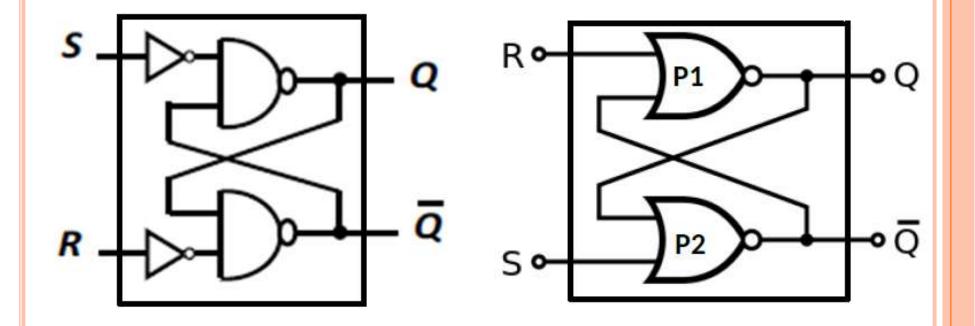

Internal structure

Internal structure

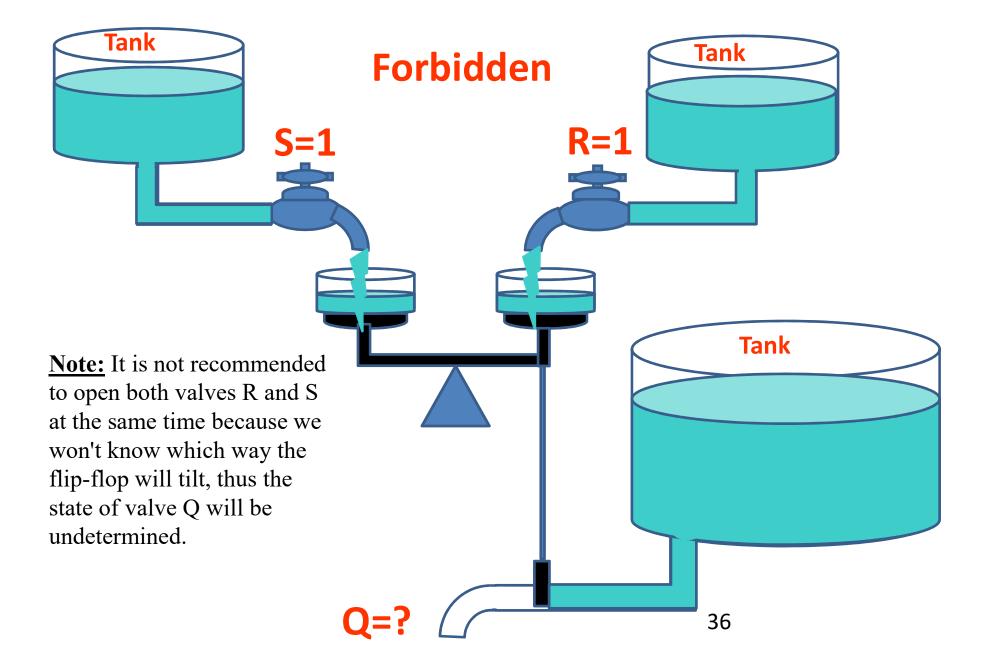

Remember that the purpose of a flip-flop is to fulfill the memory function.

We will use the two inputs R and S to set the flip-flop to '1' or '0'.

When both R and S are '0', the flip-flop should remember its previous state.

You will see that we will avoid setting both R and S to '1' at the same time.

Internal structure

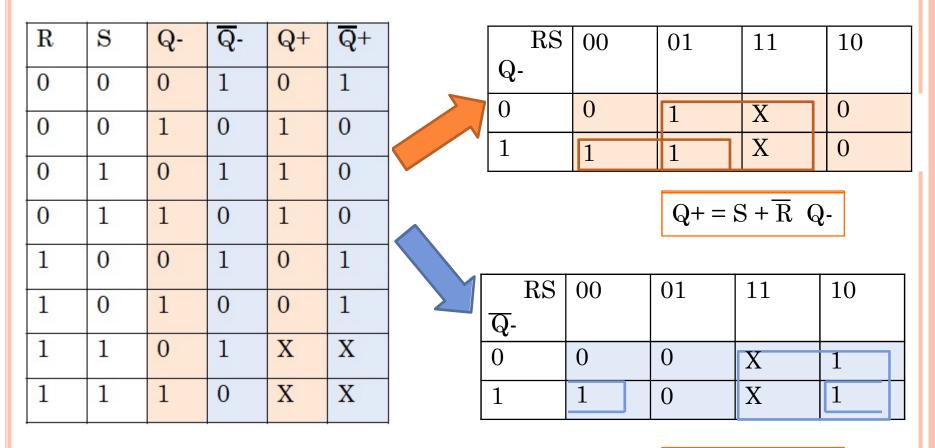

Let's verify this operation by analyzing the RS flip-flop circuit based on NOR gates:

We can represent the function Q as:

- two states Q+ and Q.

- Q+ indicating the future state of the flip-flop and Q indicating its present state.

- Thus, we can write Q + = f(R, S, Q).

#### Internal structure

$\overline{\mathbf{Q}}$ + = R +  $\overline{\mathbf{S}}$   $\overline{\mathbf{Q}}$ -

Internal structure

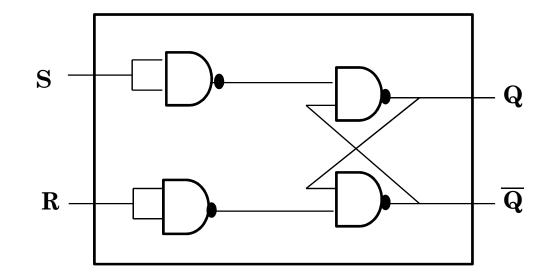

Exercise 1: Implement the RS flip-flop using only NAND gates.

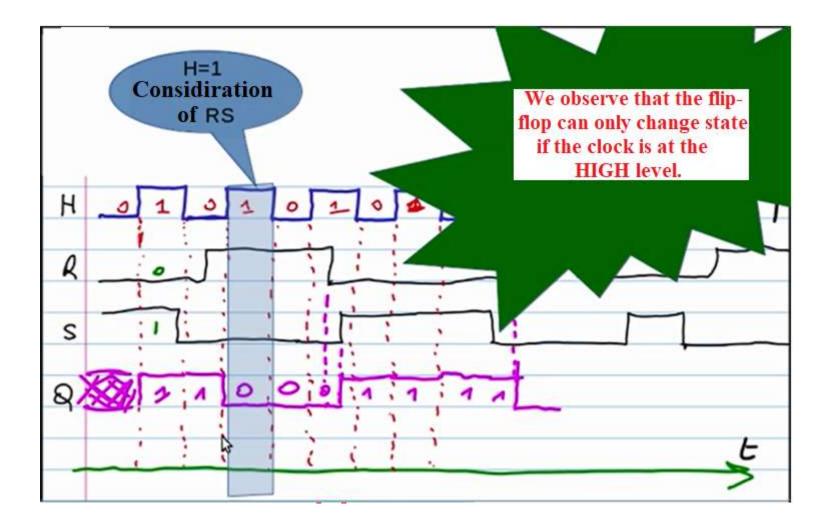

#### SYNCHRONOUS FLIP-FLOPS

The change of state of an output in a synchronous sequential system depends on the state of the control inputs and that of the active synchronization signal called the clock signal.

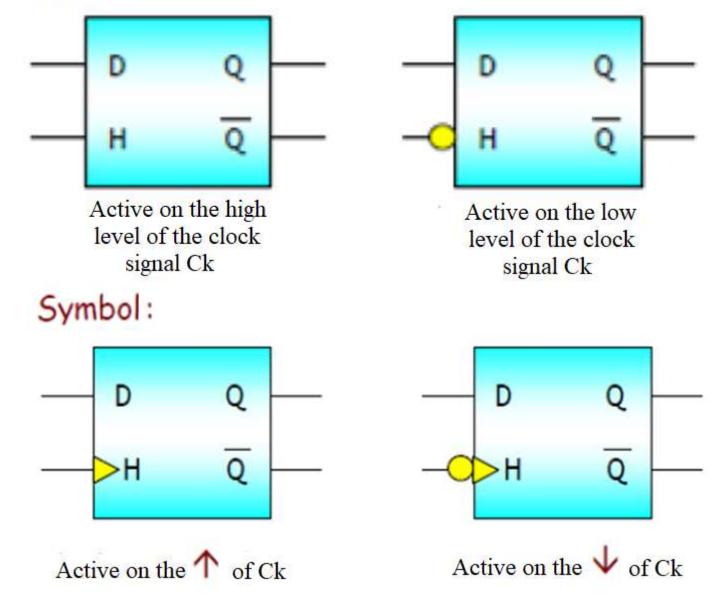

# Clock Signal Modes of Operation:

There are four modes of clock signal operation known by the following symbols (see figure):

| Symbol | Designation  |

|--------|--------------|

|        | High level   |

|        | Low level    |

|        | Rising edge  |

| ł      | Falling edge |

#### SYNCHRONOUS FLIP-FLOPS

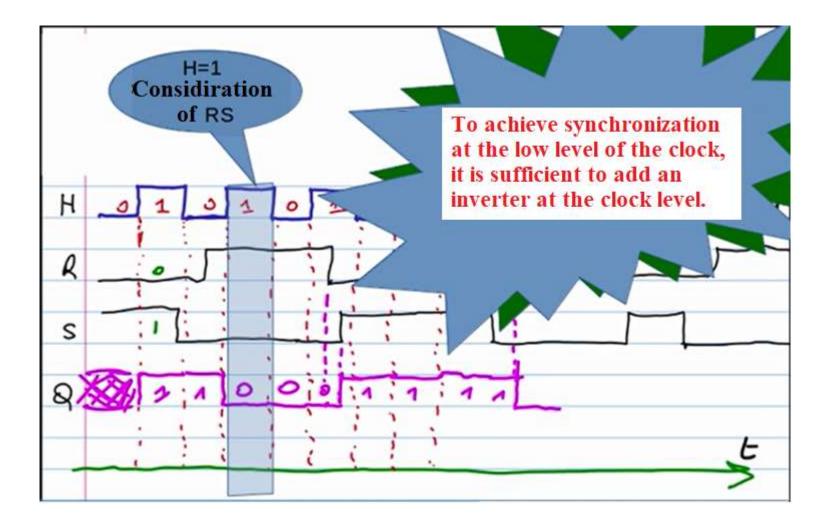

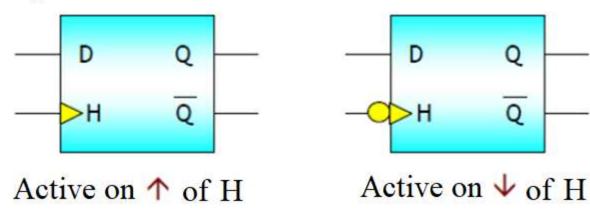

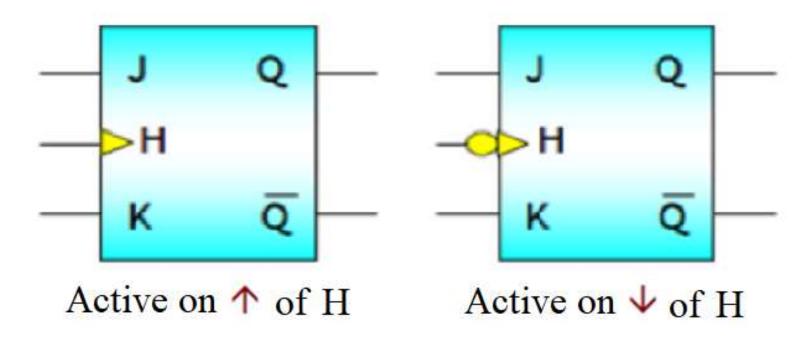

According to the clock signal mode of operation, we distinguish two families of flip-flops:

- Level-triggered flip-flops (high-level or low-level control): The flip-flop is said to be controlled statically (active on high-level or active on low-level).

- Edge-triggered flip-flops (rising edge or falling edge control): The flip-flop is said to be controlled dynamically (active on rising edge or active on falling edge).

# SYNCHRONOUS FLIP-FLOPS Symbol:

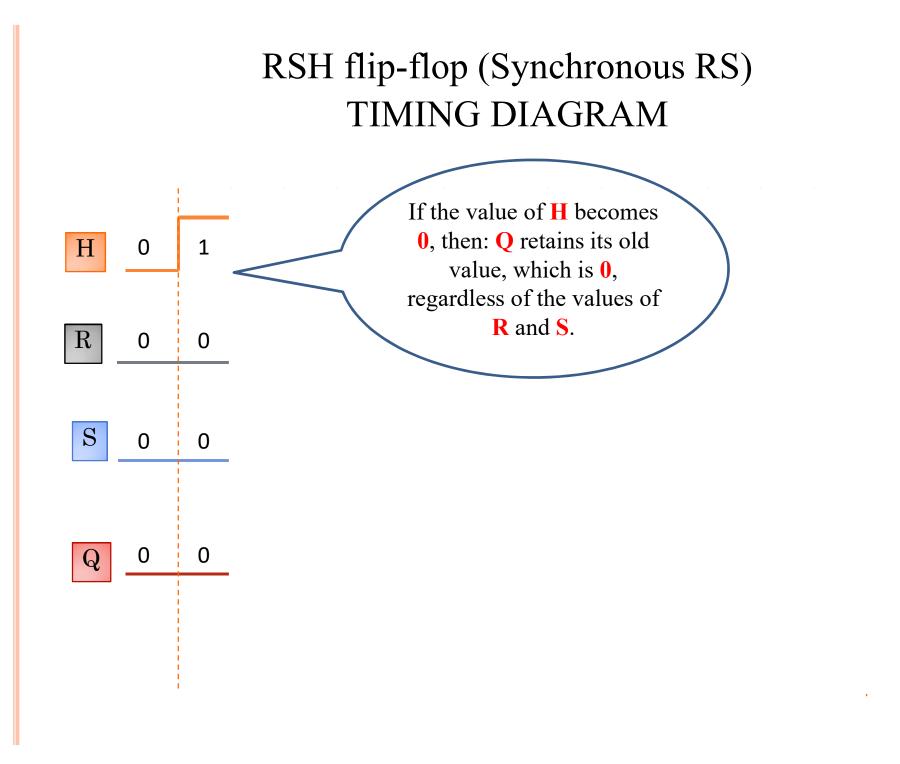

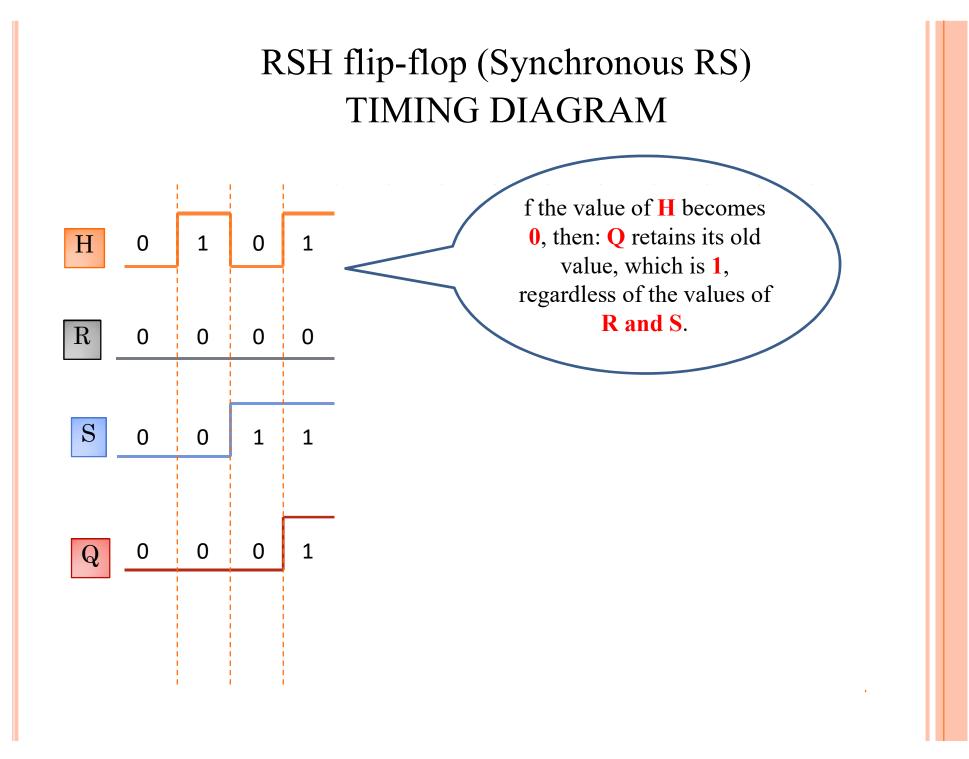

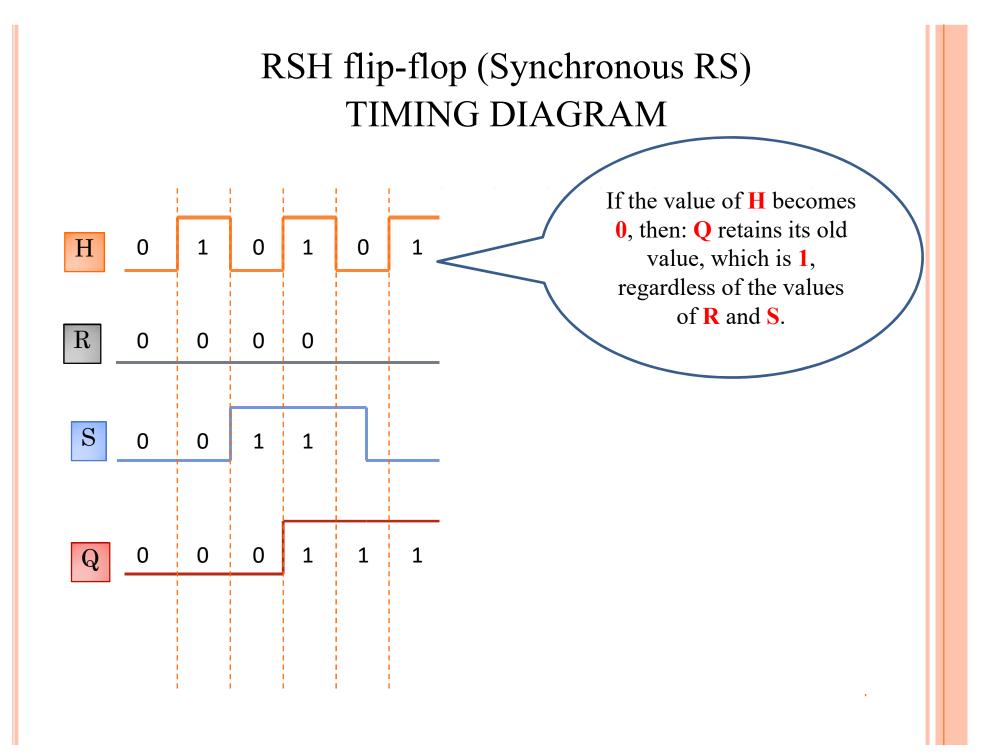

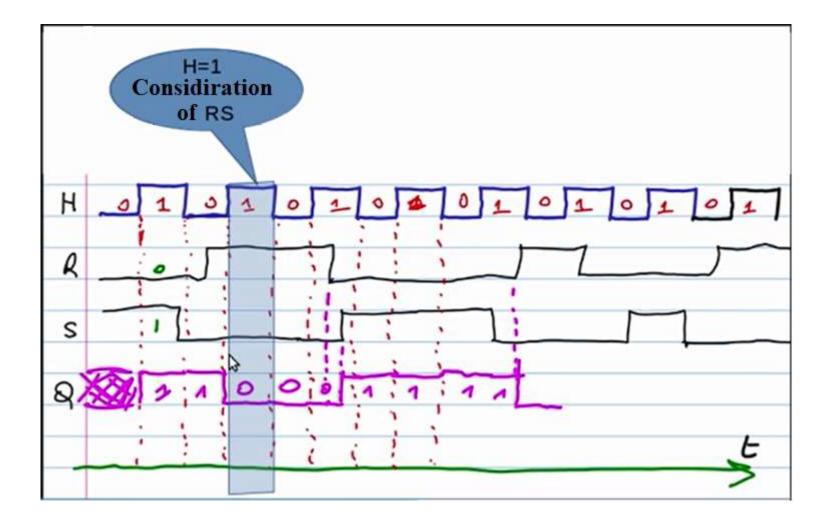

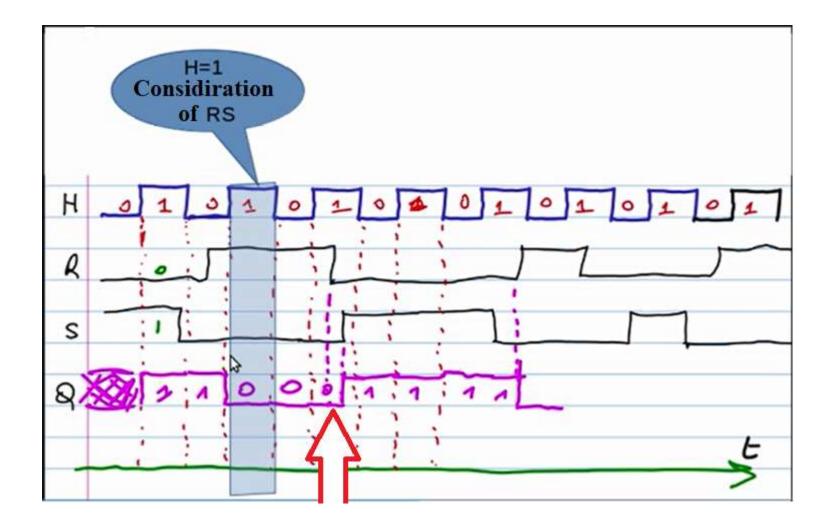

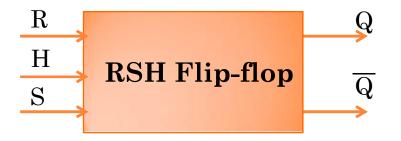

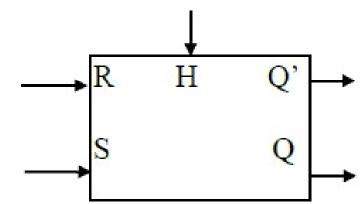

# SYNCHRONOUS FLIP-FLOPS RSH

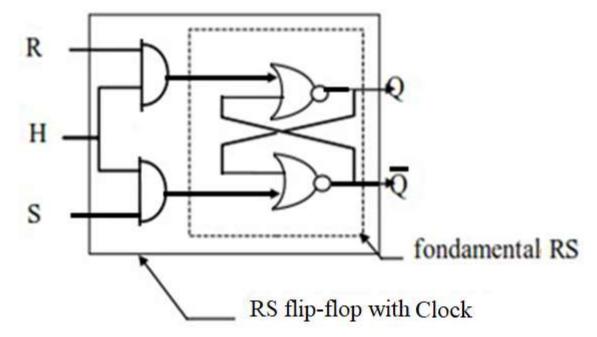

Synchronous RSH or RST Flip-Flop (RS with enable) We can easily modify the RS flip-flop to make it synchronous, meaning that changes are only allowed when the clock signal is high (or low).

The RSH flip-flop is a flip-flop where the inputs S and R are only taken into account in coincidence with a control signal.

This signal can be provided <u>by a clock</u>, thus creating a synchronous flip-flop.

Therefore, the RSH flip-flop is an RS flip-flop whose Set and Reset commands only change the state of the output Q after the authorization of a clock signal H (Clock CK). RSH Flip-Flop: RS flip-flop with a clock signal

The RSH flip-flop is a: synchronized RS flip-flop with a clock signal H.

| Н | R | S | Q+ |              |

|---|---|---|----|--------------|

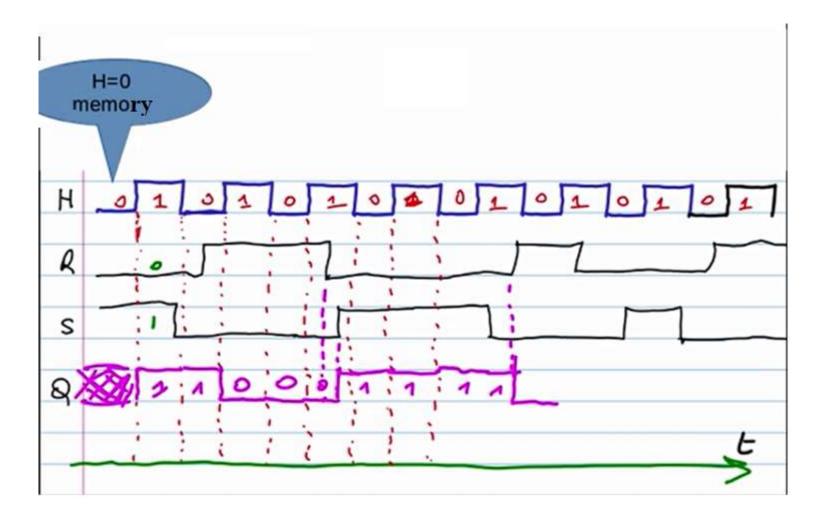

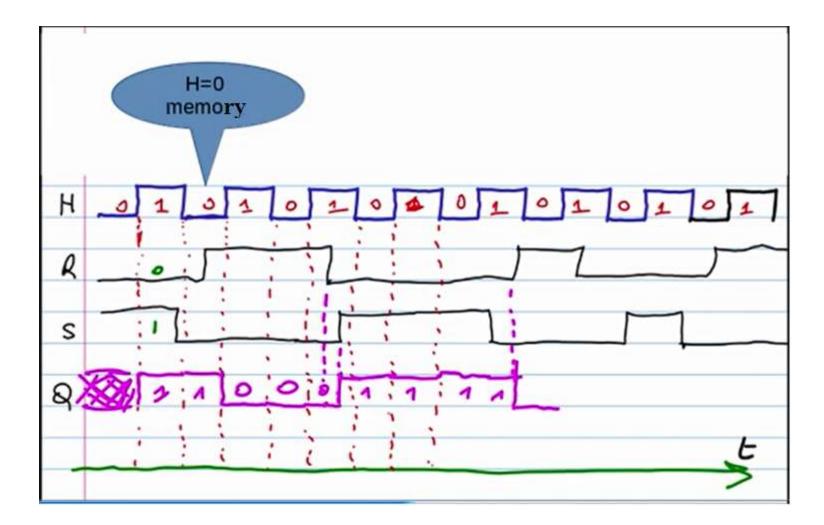

| 0 | X | X | Q- | Memory       |

| 1 | 0 | 0 | Q- |              |

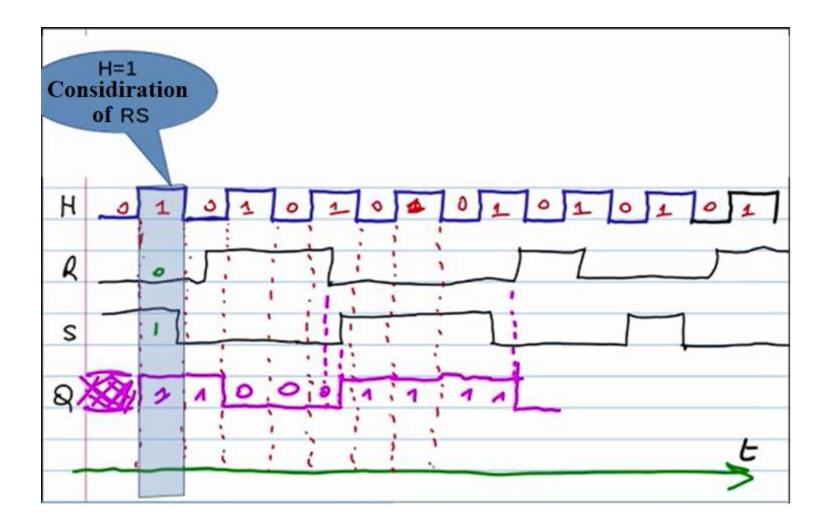

| 1 | 0 | 1 | 1  | RS Flip-Flop |

| 1 | 1 | 0 | 0  |              |

| 1 | 1 | 1 | X  |              |

# Types de synchronisations

Several ways to consider changes in the state of flip-flops:

- High-level clock: we consider the flip-flop inputs when the clock level is high (at '1').

- Low-level clock: we consider the flip-flop inputs when the clock level is low (at '0').

- Rising clock edge. Falling clock edge.

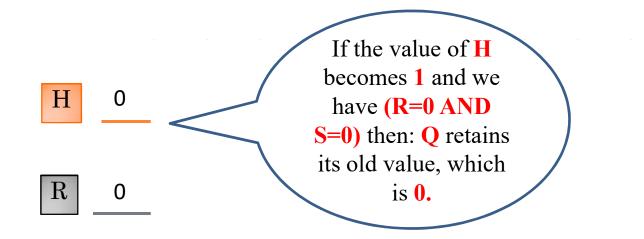

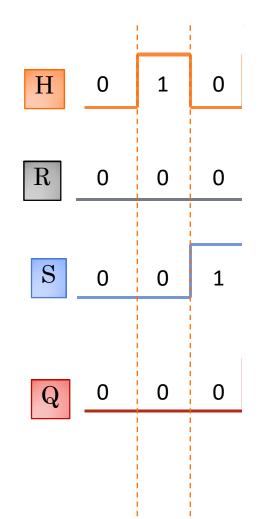

S 0

Q 0

.

. . . .

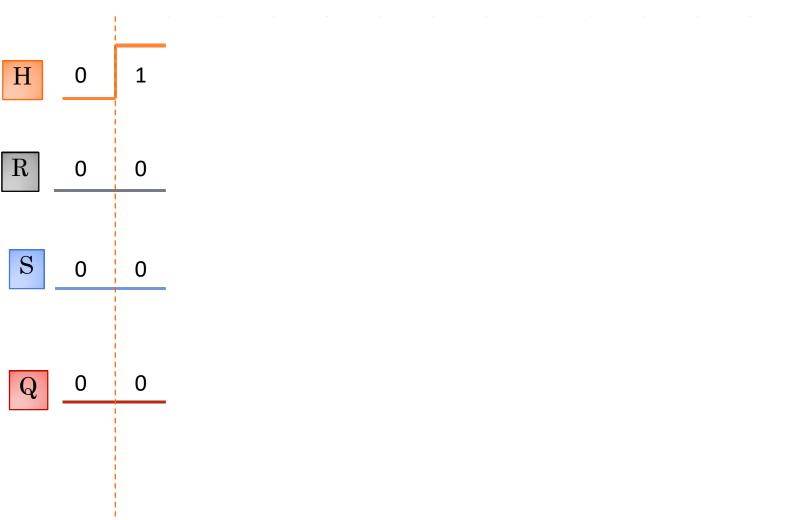

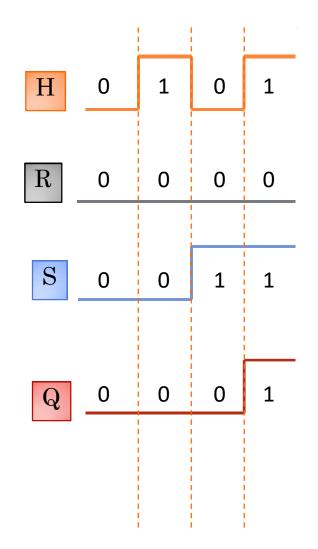

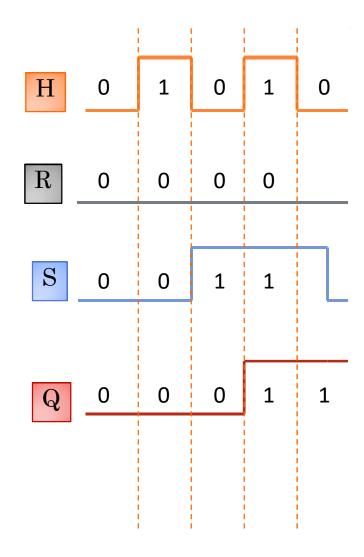

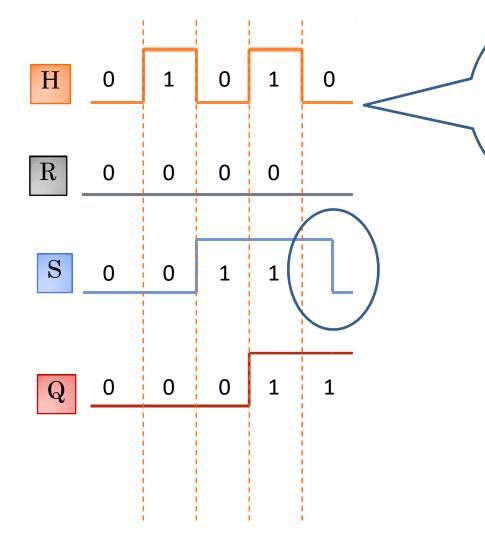

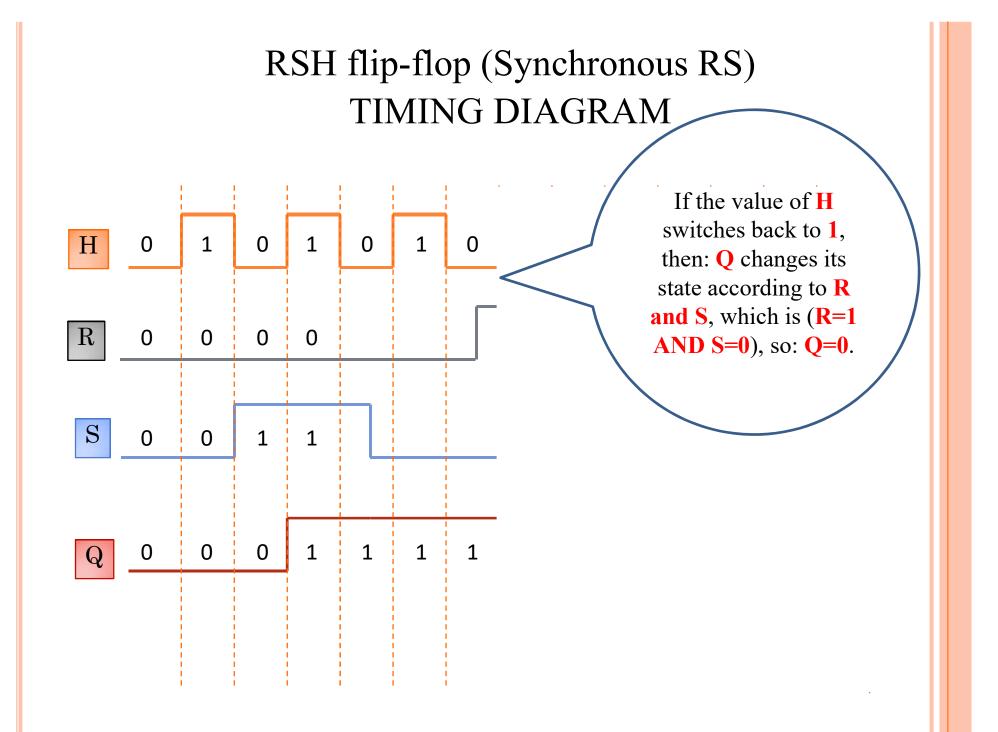

If the value of **H** switches back to **1**, then: **Q** changes its state according to **R** and **S**, which is (**R=0 AND S=0**), so: **Q** retains its old value, which is **1**.

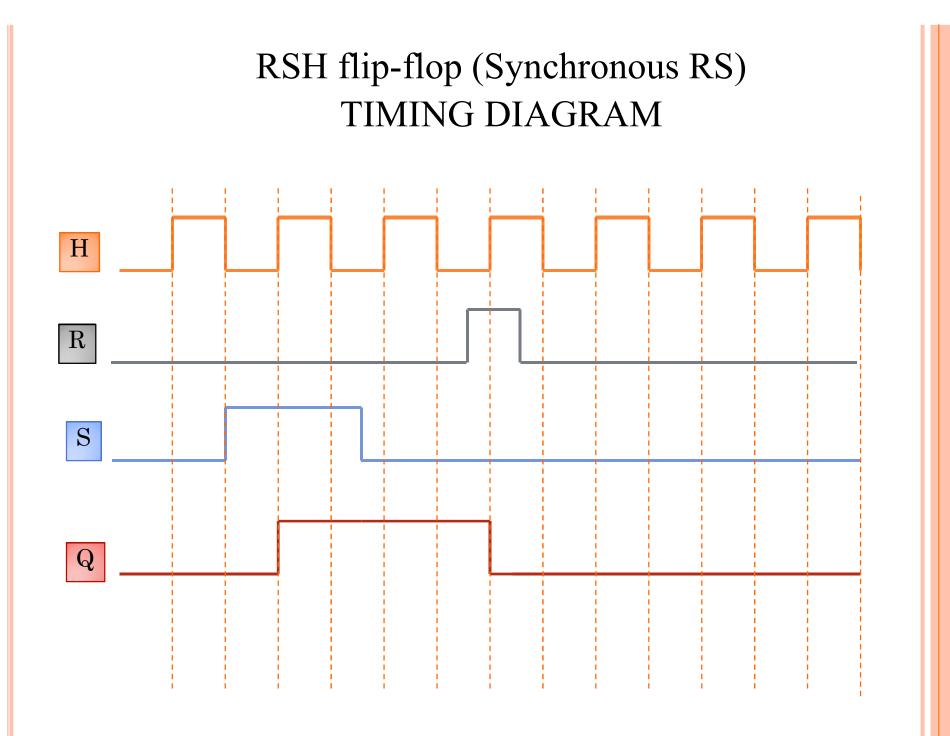

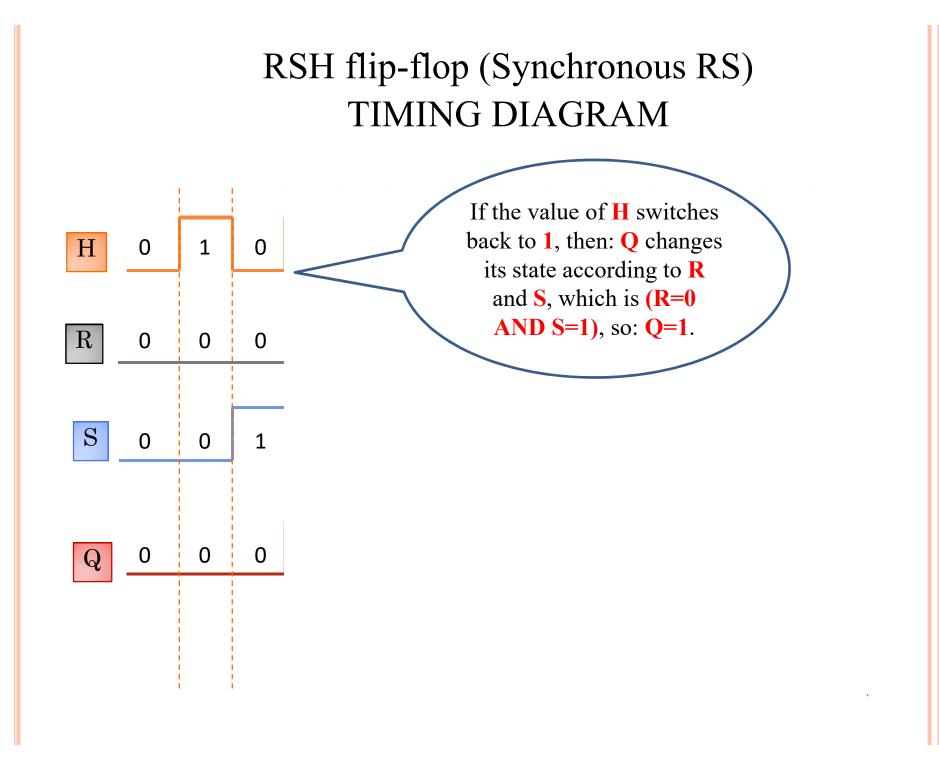

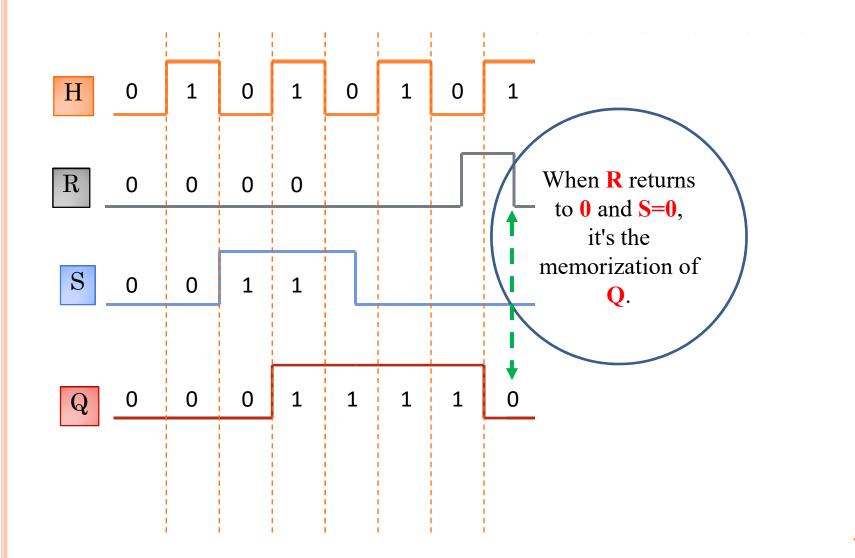

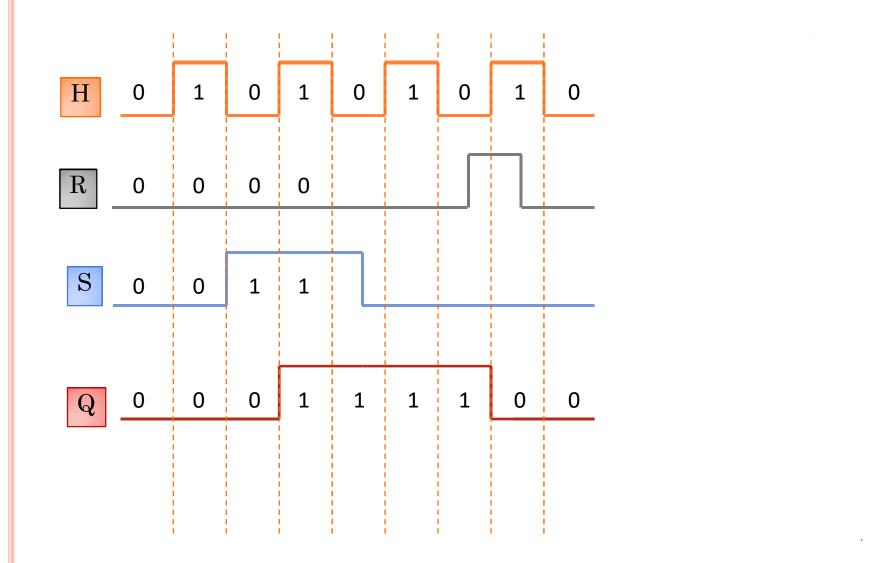

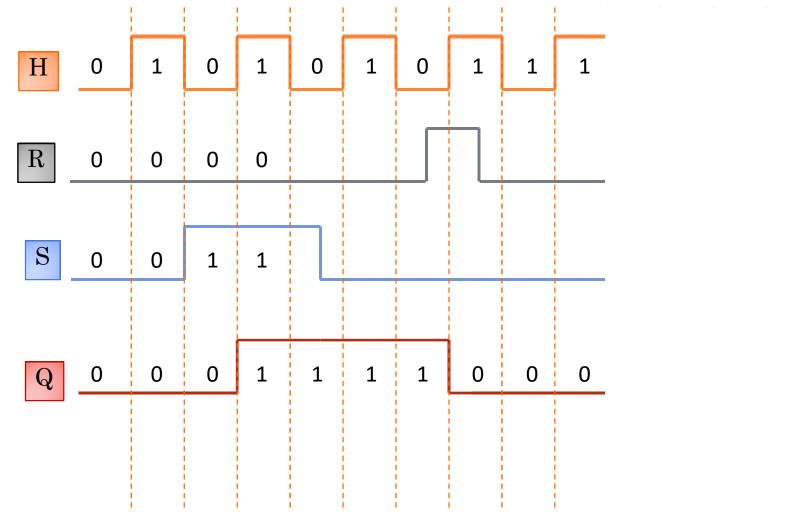

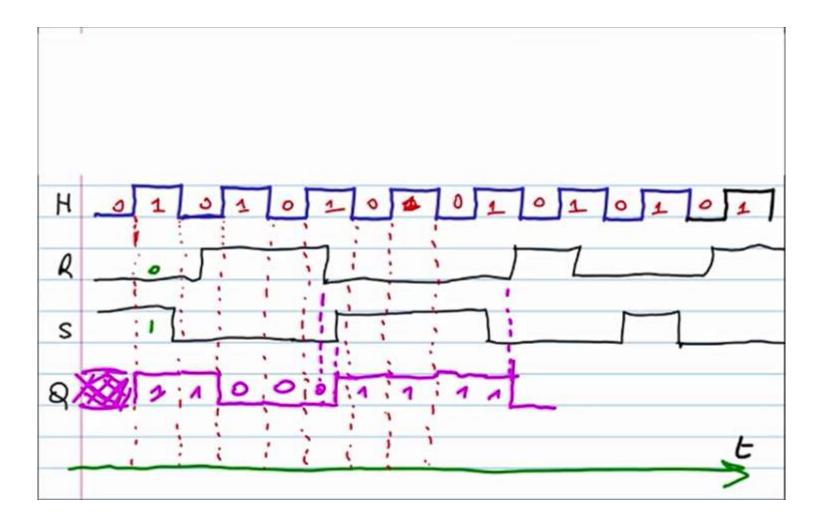

#### RSH flip-flop (Synchronous RS) EXAMPLE: TIMING DIAGRAM

RSH flip-flop (Synchronous RS)

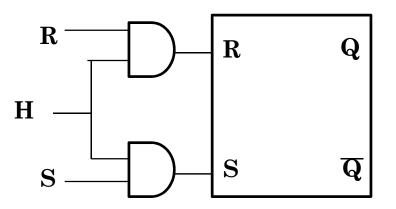

**Exercise 2:** Provide the circuit of this RSH flip-flop using the RS flip-flop.

**Solution:** Simply create a logical AND between its inputs and the clock signal, to ensure that the consideration of its inputs is synchronized by the clock signal.

#### RSH flip-flop (Synchronous RS)

**Exercise 2:** Provide the circuit of this RSH flip-flop using the RS flip-flop.

Schematically, the RS flip-flop is represented as follows:

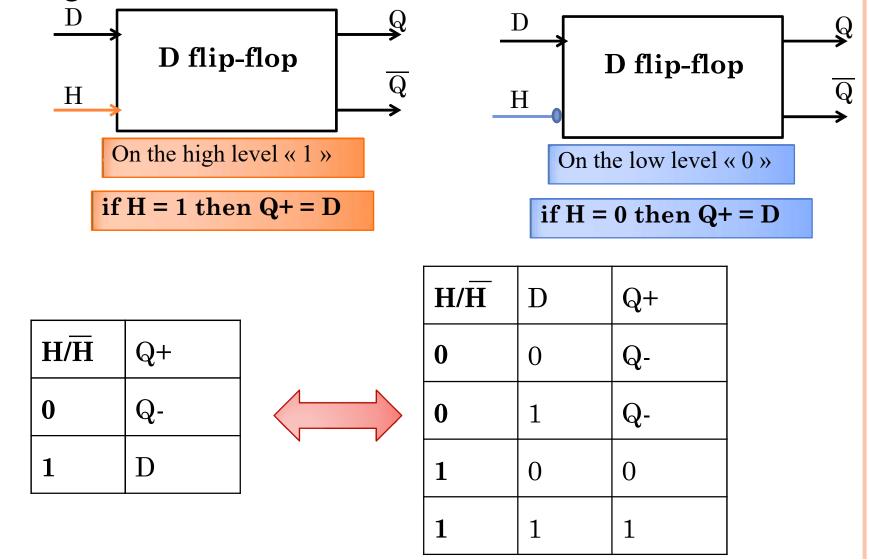

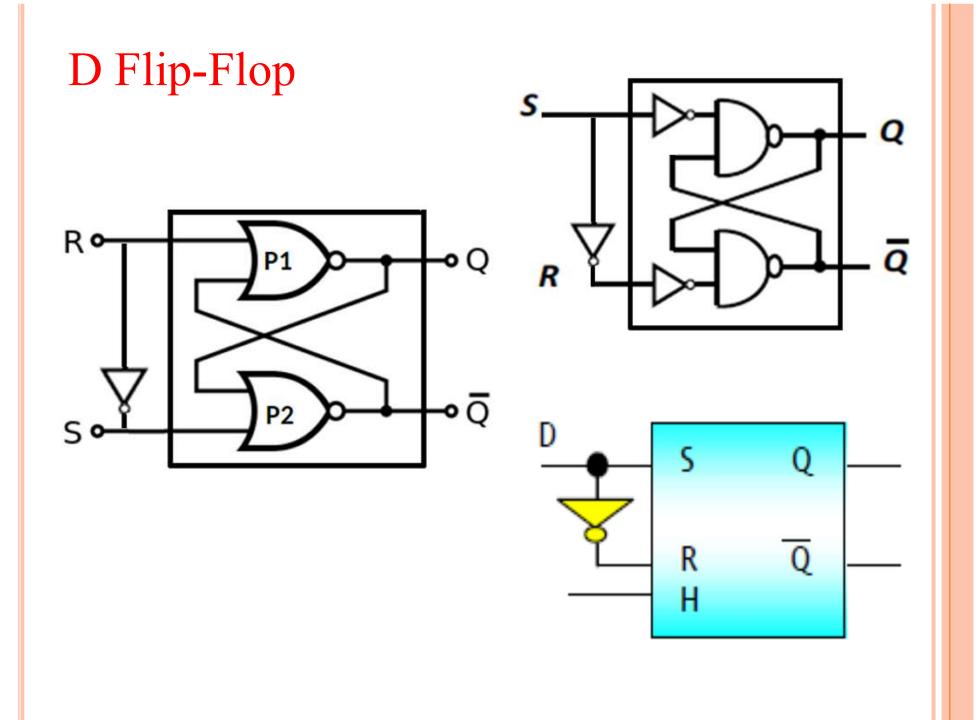

#### D flip-flop

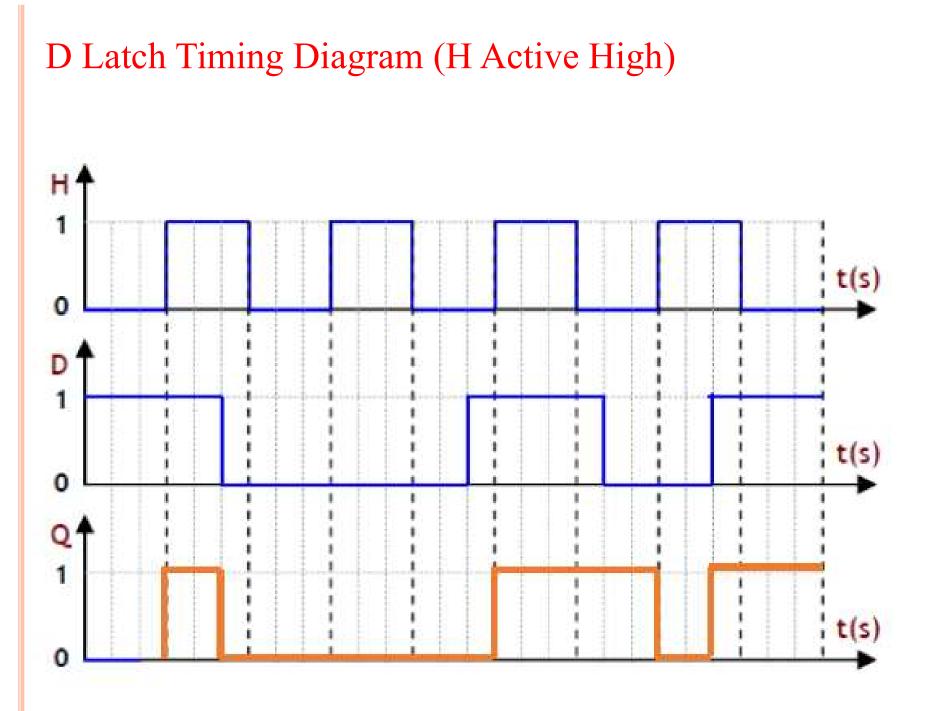

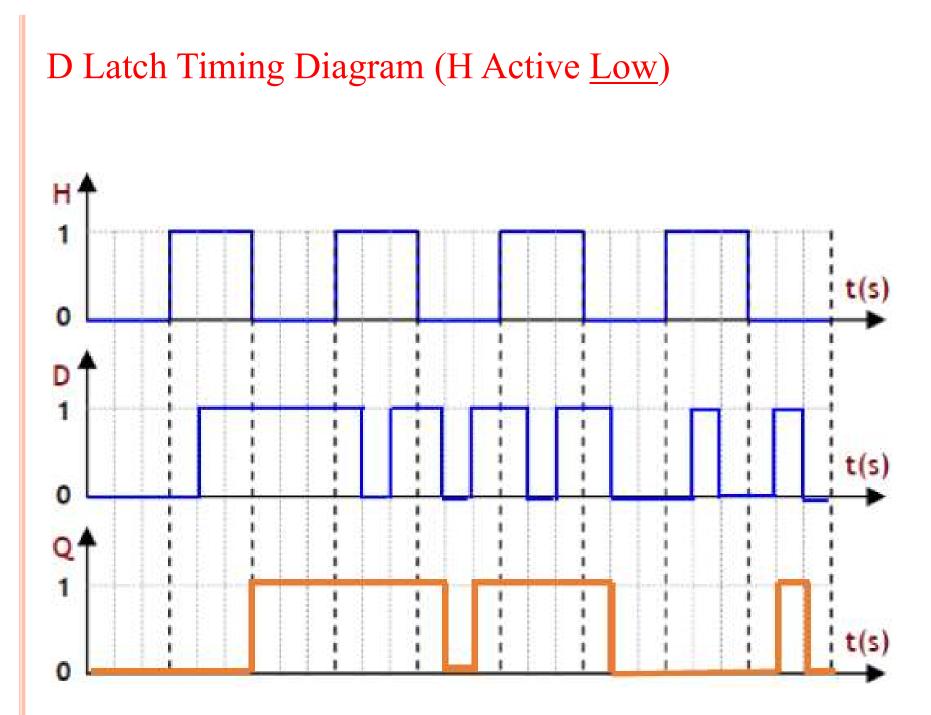

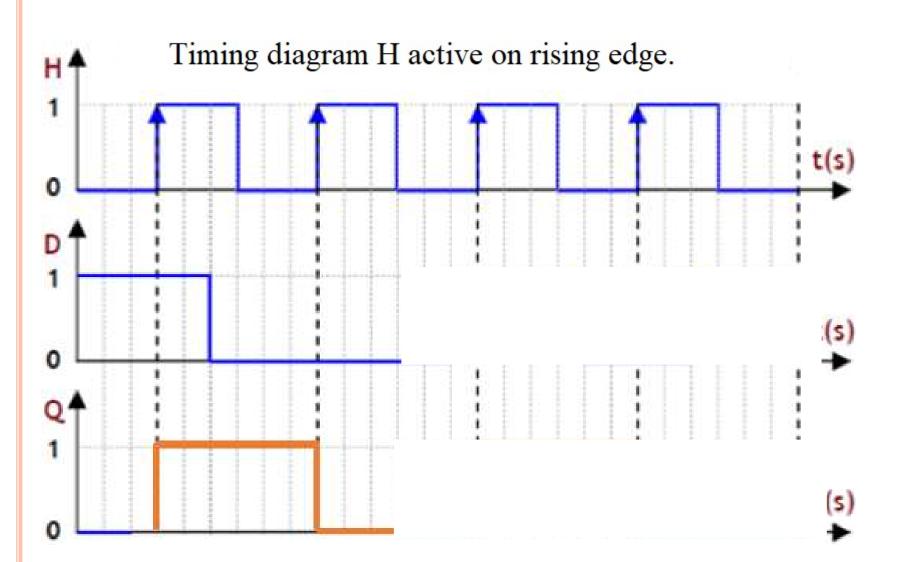

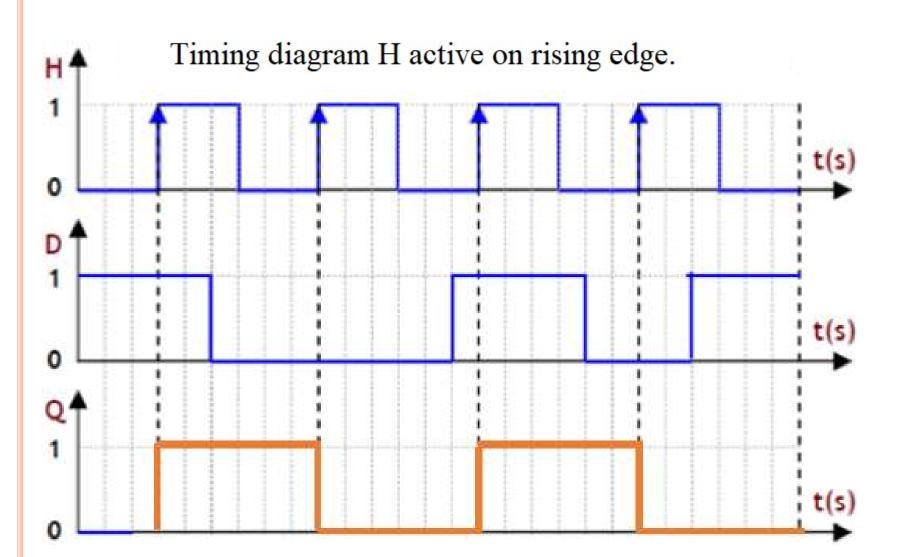

**<u>D Flip-Flop:</u>** That's a synchronous latch triggered by either the high or low level.

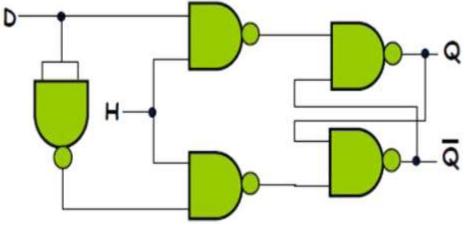

# D Flip-Flop

The D flip-flop (Data or Datum) is derived from the RSH flip-flop by adding an <u>inverter gate</u> between the Set and Reset inputs to have only one input to determine the logical level to be memorized. With this flip-flop, there is no longer an invalid combination of S=R=1 (Under these conditions, the state R=S=1, which led to ambiguous operation, can no longer exist).

Two types of D flip-flops are distinguished:

Level-triggered D flip-flop (Static).

Edge-triggered D flip-flop (Dynamic),

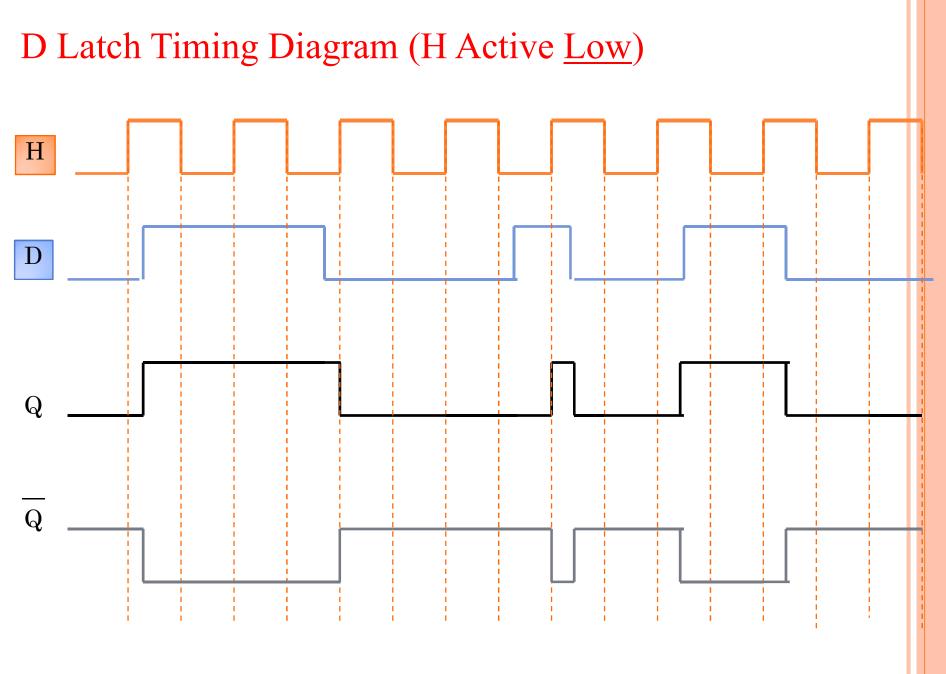

#### D latch or Latch D Flip-Flop (Latch: Lock)

The D flip-flop is an RSH flip-flop whose inputs <u>**R** and S are complemented</u> in order to eliminate the forbidden state (R=S=1) and minimize the number of memory states.

- ➤ When H is active and D=1: the output Q will be set to 1 (set).

- When H is active and D=0: the output Q will be reset to 0 (reset).

- $\blacktriangleright$  When H is not active:

the outputs remain in the previous state (memory).

It's a synchronous static flip-flop triggered by the <u>clock signal level</u>, operating as follows:

- The flip-flop is transparent as long as the clock signal is at the high level (or low level).

The output Q follows all variations of the input D.

The latch is said to be transparent.

- The state of the output Q is locked (memorized) as long as the clock signal is at the low level (or high level).

The output **Q** retains its logical state. The latch is said to be latched.

|   | Truth table |   |                                          |  |

|---|-------------|---|------------------------------------------|--|

| Н | D           | Q | Comment                                  |  |

| 0 | x           | 9 | Memorization                             |  |

| 1 | 0           | 0 | the latch copies the value<br>of D to Q. |  |

| 1 | 1           | 1 |                                          |  |

- When H = 1, the output Q is identical to D (Q=D); this is referred to as the latch being transparent.

- When H = 0, the output Q remains at the last value of D it had before H transitioned to 0. In other words, the output is 'latched' to D and does not change as long as CLK remains at the low level, even if D changes value.

The operation of the D latch is summarized in the following truth table.

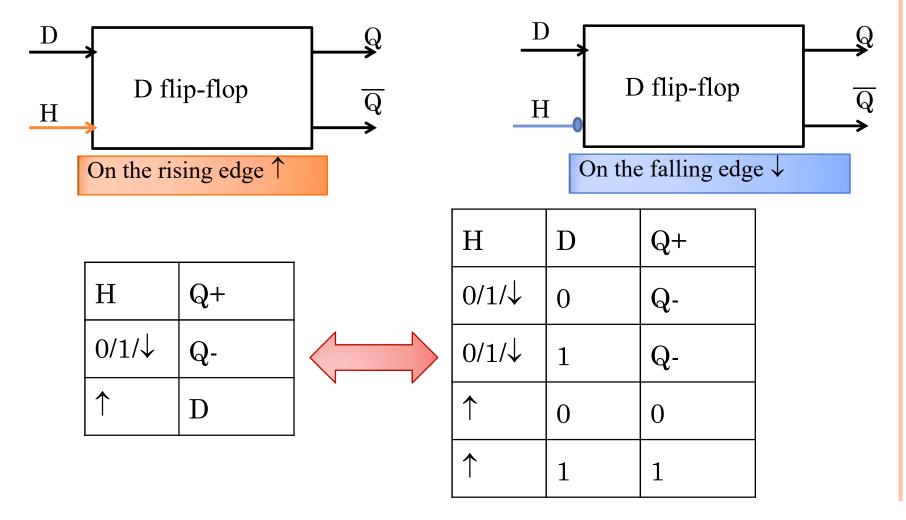

#### D flip-flop

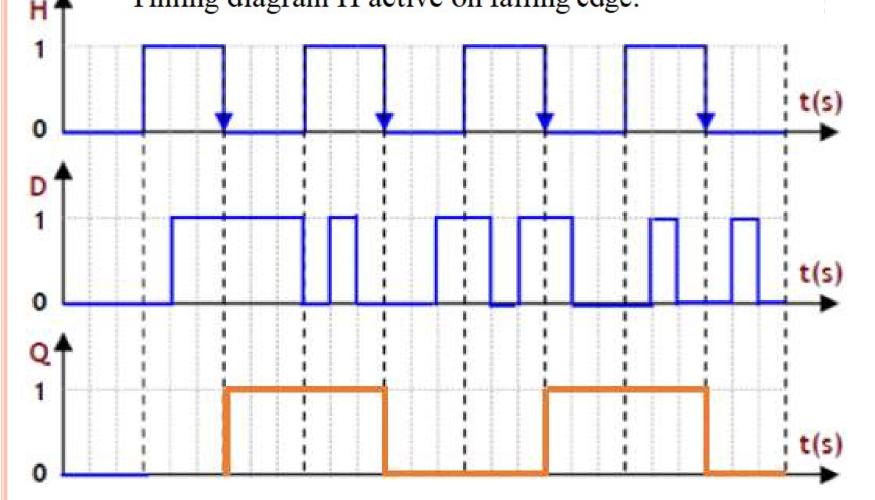

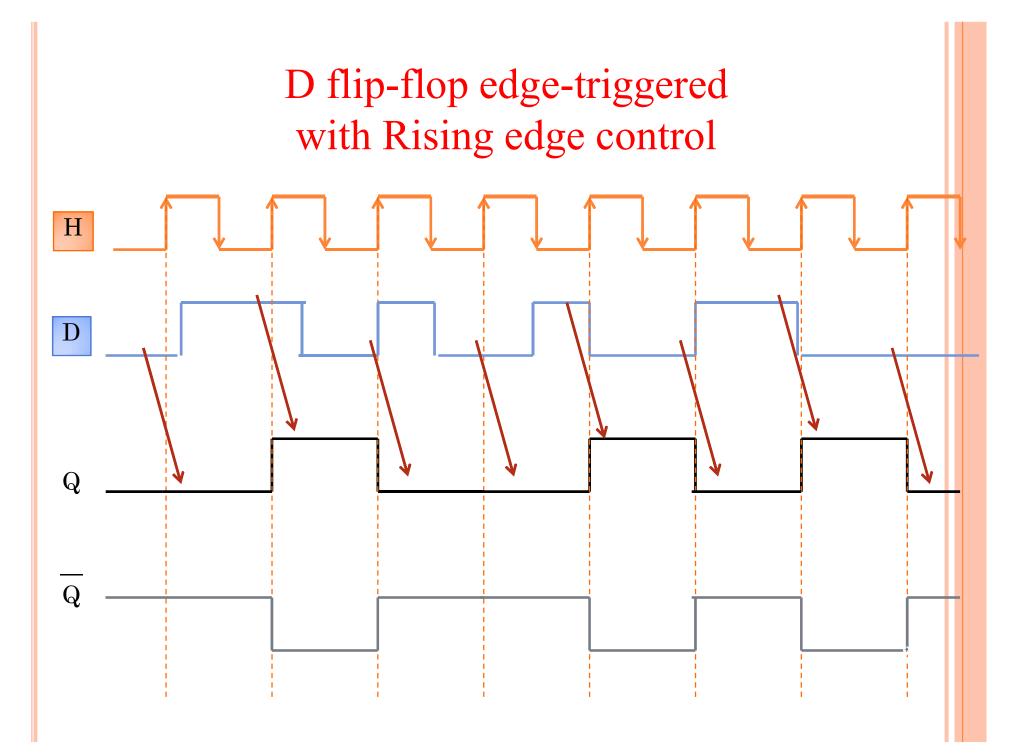

It's a flip-flop synchronized on the rising edge or the falling edge.

# D flip-flop

Exercise 3: Transform an RSH flip-flop to act as a D latch (active high)

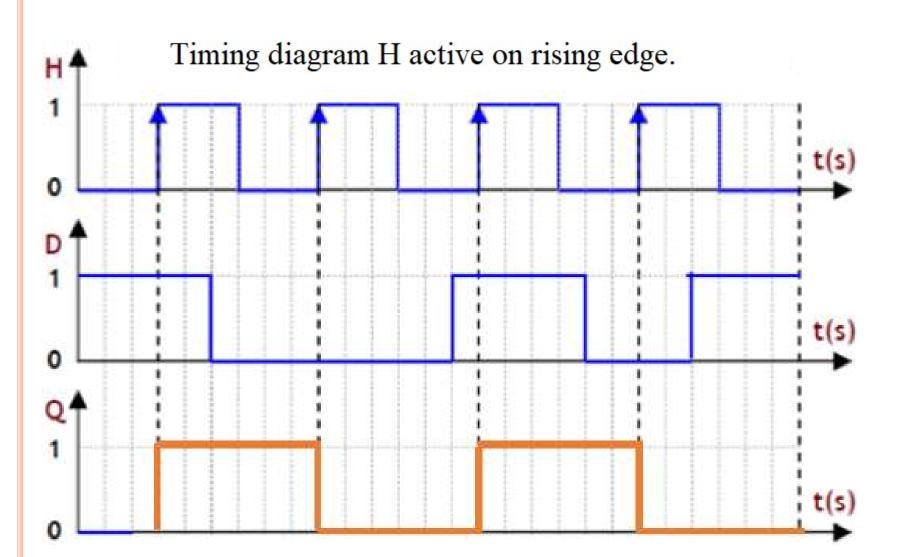

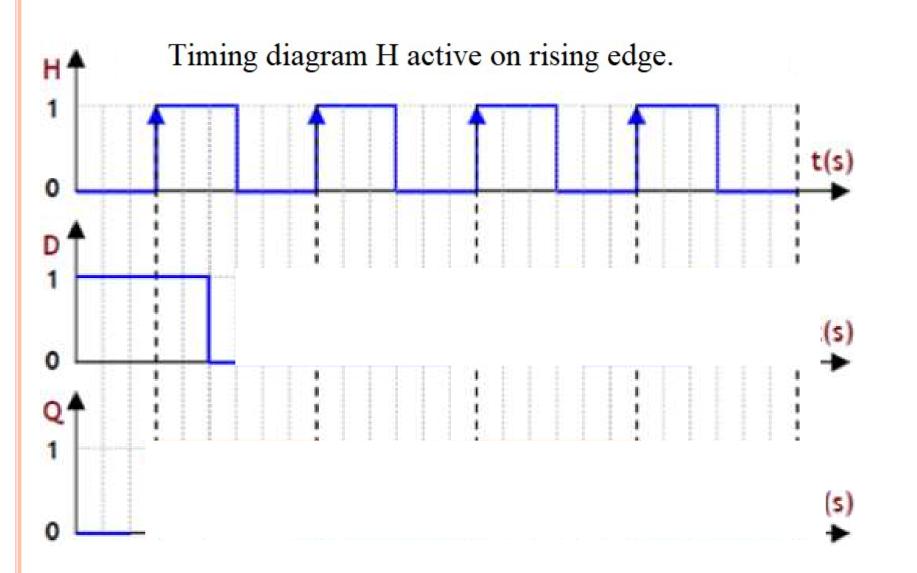

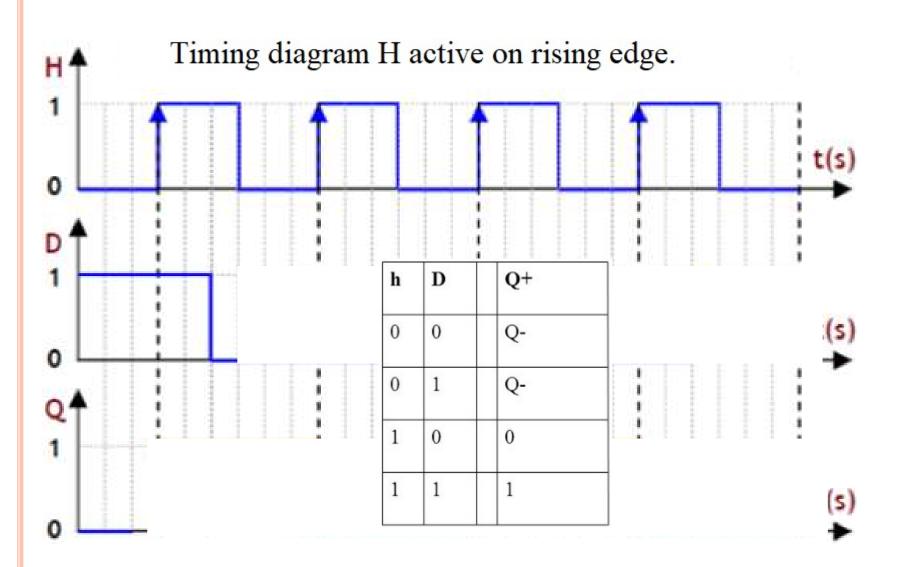

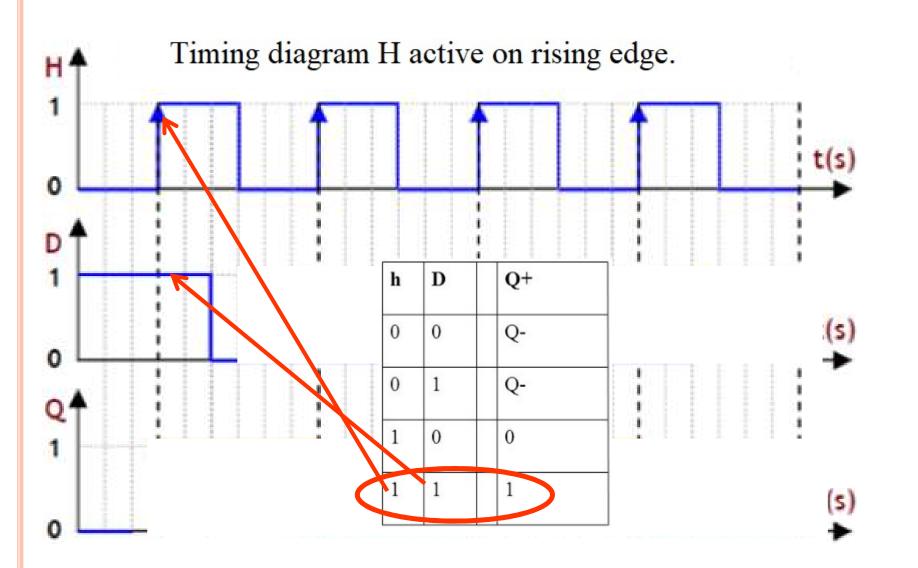

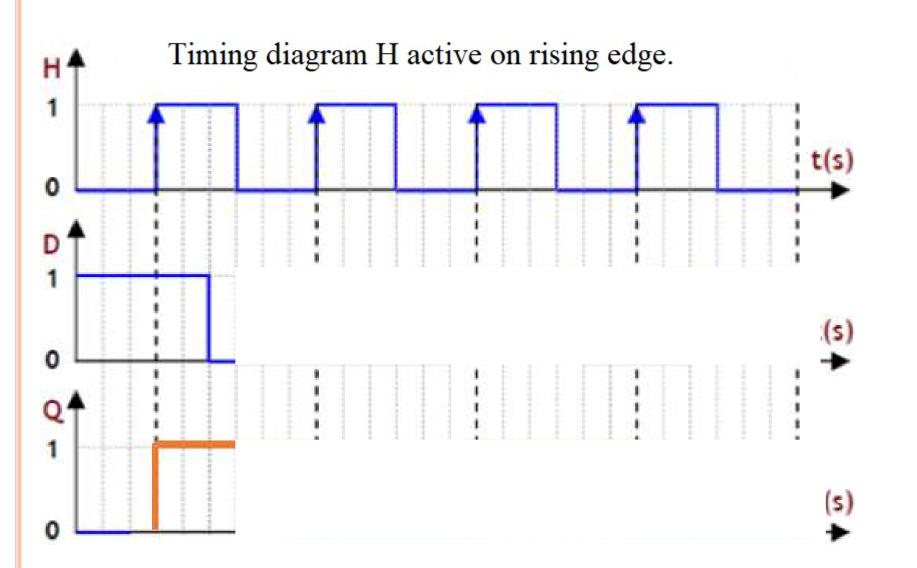

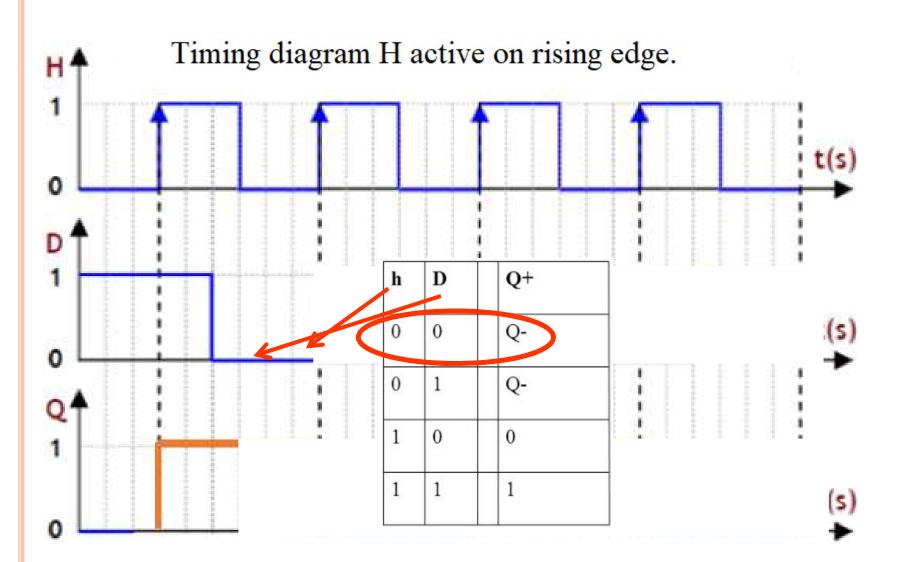

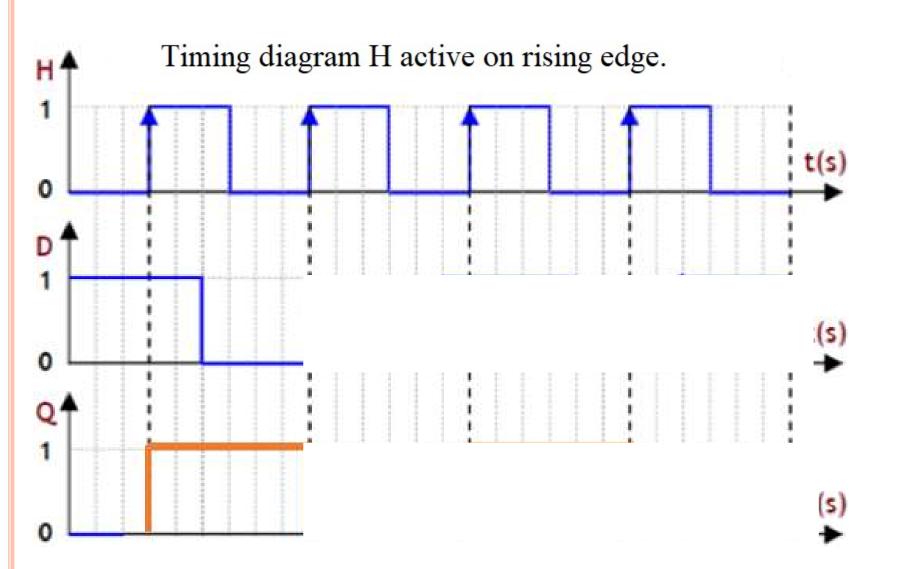

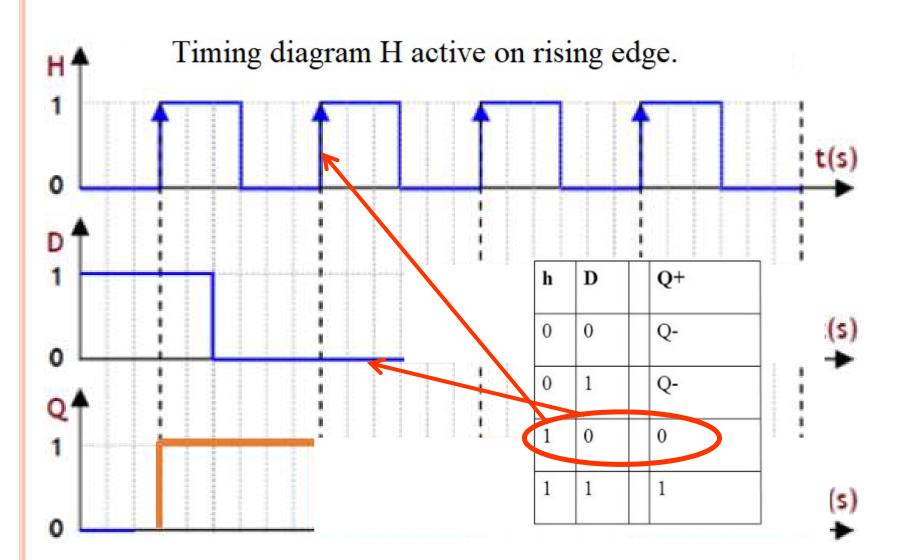

| Н | D | Q+ |

|---|---|----|

| 0 | 0 | Q- |

| 0 | 1 | Q- |

| 1 | 0 | 0  |

| 1 | 1 | 1  |

| Н | R | S | Q+ |

|---|---|---|----|

| 0 | X | X | Q- |

| 1 | 0 | 0 | Q- |

| 1 | 0 | 1 | 1  |

| 1 | 1 | 0 | 0  |

| 1 | 1 | 1 | X  |

$H_D = H_{RSH}, R = \overline{D}; S = D$

This is a synchronous dynamic flip-flop on the clock edge, operating as follows:

In the <u>presence</u> of the active clock edge, the flip-flop copies the logical state of input **D** to output **Q**. In the <u>absence</u> of the active clock edge, the flip-flop retains its logical state at output **Q**.

Symbol :

# A D flip-flop or an edge-triggered flip-flop with falling edge control.

Timing diagram H active on falling edge.

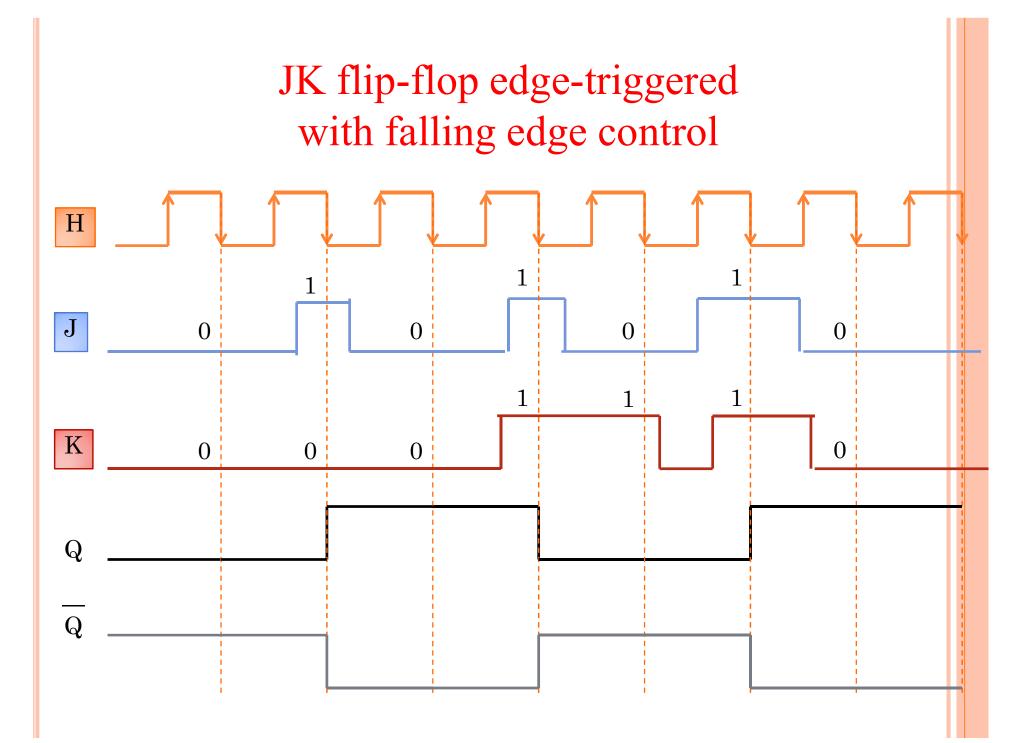

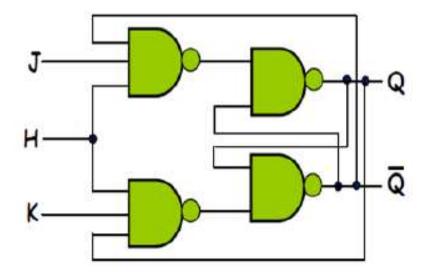

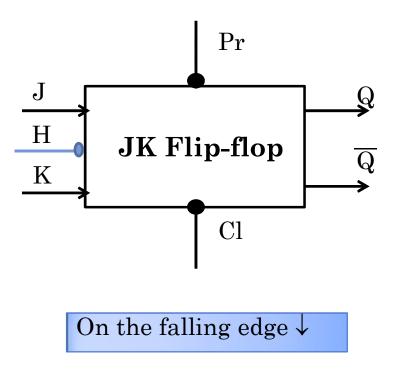

#### JK flip-flop

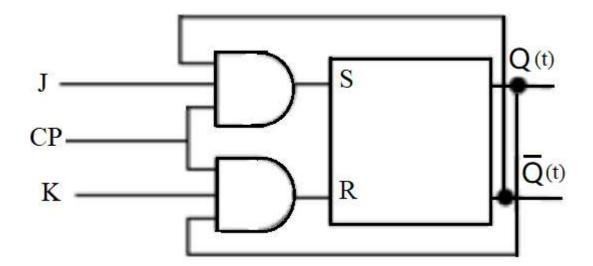

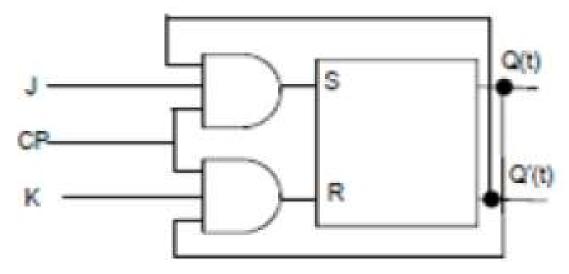

The JK flip-flop is an improvement over the RS flipflop. The undetermined case of the latter (S and R both equal to 1) is defined in the JK flip-flop by inverting the states of the outputs by connecting the inputs R and S to the outputs.  $S=J\bar{q}$  et R=Kq

## JK flip-flop

The JK flip-flop thus <u>eliminates the ambiguity</u> that exists for the combination S=R=1 in the RSH flip-flop.

|     | Output equation |    |    |    |  |  |

|-----|-----------------|----|----|----|--|--|

| °.' | K 00            | 01 | 11 | 10 |  |  |

| 0   | 0               | 0  | 1  | 1  |  |  |

| 1   | 1               | 0  | 0  | 1  |  |  |

$Q(t+1) = J\overline{Q} + \overline{K}Q$

## JK flip-flop

The JK flip-flop thus <u>eliminates the ambiguity</u> that exists for the combination S=R=1 in the RSH flip-flop.

| Comment        | Comment | Q(t+1) | R | s | Q(t) | K | J |

|----------------|---------|--------|---|---|------|---|---|

| No change,     |         | Q(t)   | 0 | 0 | 0    | 0 | 0 |

|                | Q(t)    | Q(t)   | 0 | 0 | 1    | 0 | 0 |

| Reset to 0     |         | Q(t)=0 | 0 | 0 | 0    | 1 | 0 |

|                | 0       | 0      | 1 | 0 | 1    | 1 | 0 |

| Set to 1       |         | 1      | 0 | 1 | 0    | 0 | 1 |

|                | 1       | Q(t)=1 | 0 | 0 | 1    | 0 | 1 |

| Inverted state |         | 1      | 0 | 1 | 0    | 1 | 1 |

|                | Q'(t)   | 0      | 1 | 0 | 1    | 1 | 1 |

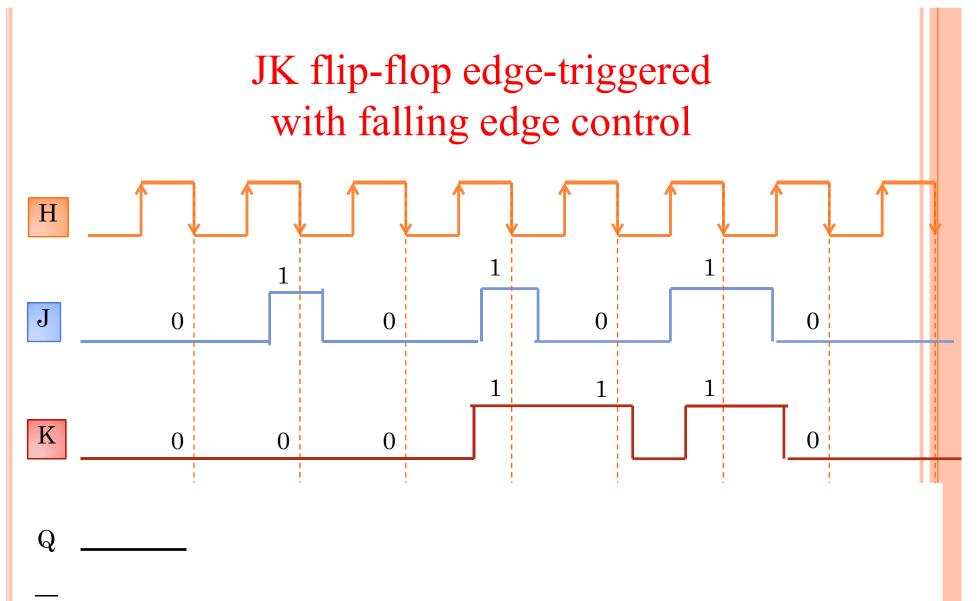

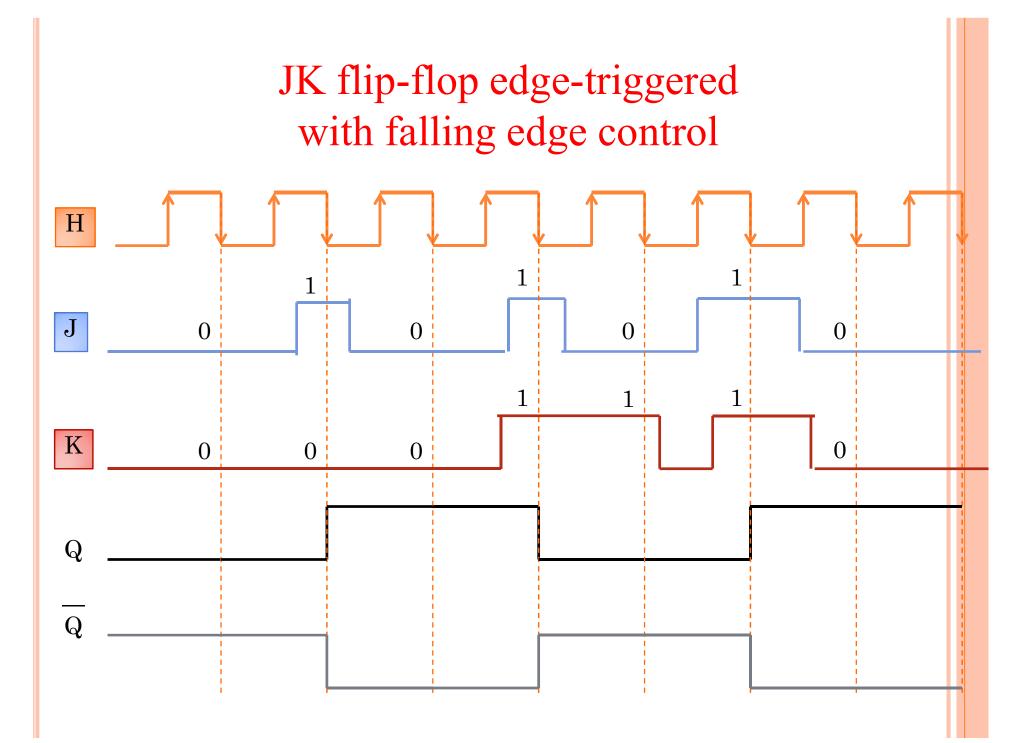

# JK Flip-flop

The JK flip-flop is a dynamic synchronous flip-flop with two inputs controlling the state of the flip-flop, and a synchronization input H:

- The J input (Jump, set to one) acts as the S input of the RSH flip-flop.

- The K input (Kill, reset to zero) acts as the R input of the RSH flip-flop.

- In the absence of the clock signal, the flip-flop retains the previous state of the output Q (memory).

- For the combination J=K=0, the flip-flop remembers the state of the output Q at each active clock edge (rising or falling edge).

# JK Flip-flop

# Symbol :

## JK Flip-flop

When J=K, the output Q copies the state of the J input at each active clock edge.

- For the combination JK=10, the output Q is set to 1 at each active clock edge.

- For the combination JK=01, the output Q is set to 0 at each active clock edge.

- With simultaneous action on J and K (J=K=1), the flip-flop changes state at each active clock edge, which is the toggle mode.

# Synchronous JK flip-flop with rising clock edge

|                 | The truth table |   |   |                           |  |  |

|-----------------|-----------------|---|---|---------------------------|--|--|

| H J K Q Comment |                 |   |   | Comment                   |  |  |

| 1               | 0               | 0 | 9 | Memory                    |  |  |

| 1               | 0               | 1 | 0 | Resetting the output Q    |  |  |

| 1               | 1               | 0 | 1 | Setting the output Q to 1 |  |  |

| 1               | 1               | 1 | q | Toggling the output state |  |  |

$\overline{\mathbf{Q}}$

#### JK flip-flop ASYNCHRONOUS

It's a variant flip-flop of RS where it takes into account the case R=S=1.

| J | K | Q+ |              |

|---|---|----|--------------|

| 0 | 0 | Q- | Memory state |

| 0 | 1 | 0  | Reset        |

| 1 | 0 | 1  | Set          |

| 1 | 1 | Q- | Switching    |

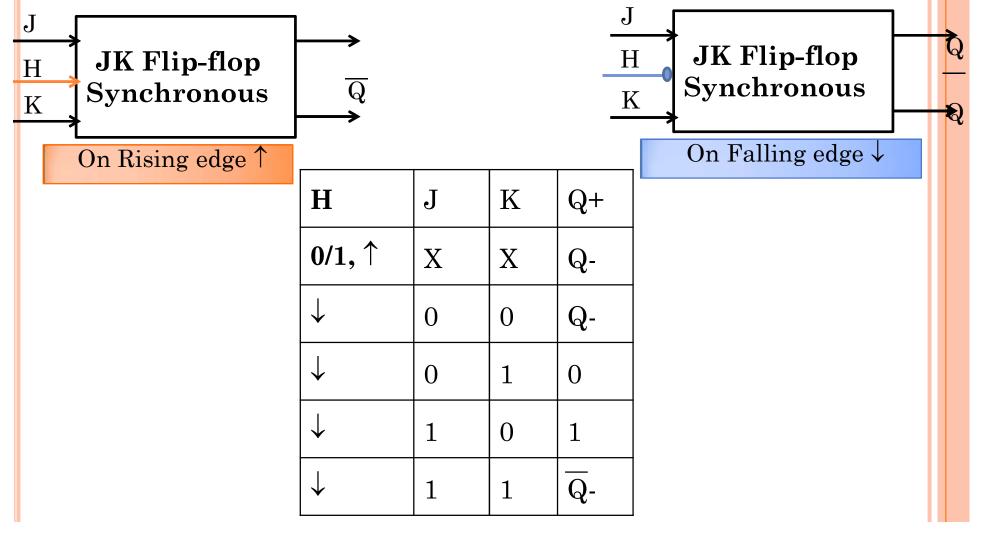

#### JK flip-flop SYNCHRONOUS

It's a flip-flop with two inputs J and K, and a Clock (rising or falling edge).

#### JK flip-flop ASYNCHRONOUS

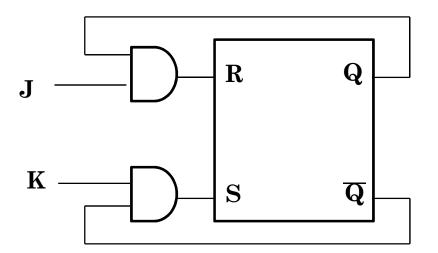

Exercise 05: Implementing an asynchronous JK flip-flop using an RS flip-flop.

#### JK flip-flop ASYNCHRONOUS

Exercise 05: Implementing an asynchronous JK flip-flop using an RS flip-flop.

| R | S | Q- | Q+ |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 0 | 1  | 1  |

| 0 | 1 | 0  | 1  |

| 0 | 1 | 1  | 1  |

| 1 | 0 | 0  | 0  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | 0  | X  |

| 1 | 1 | 1  | X  |

| J | K | Q- | Q+ |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 0 | 1  | 1  |

| 0 | 1 | 0  | 1  |

| 0 | 1 | 1  | 1  |

| 1 | 0 | 0  | 0  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | 0  | 1  |

| 1 | 1 | 1  | 0  |

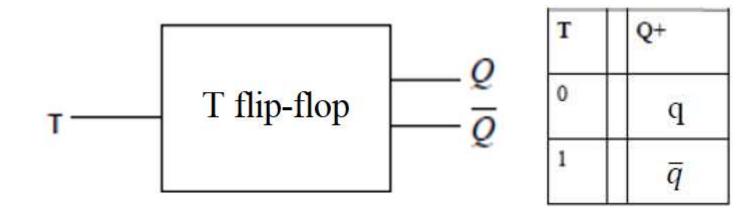

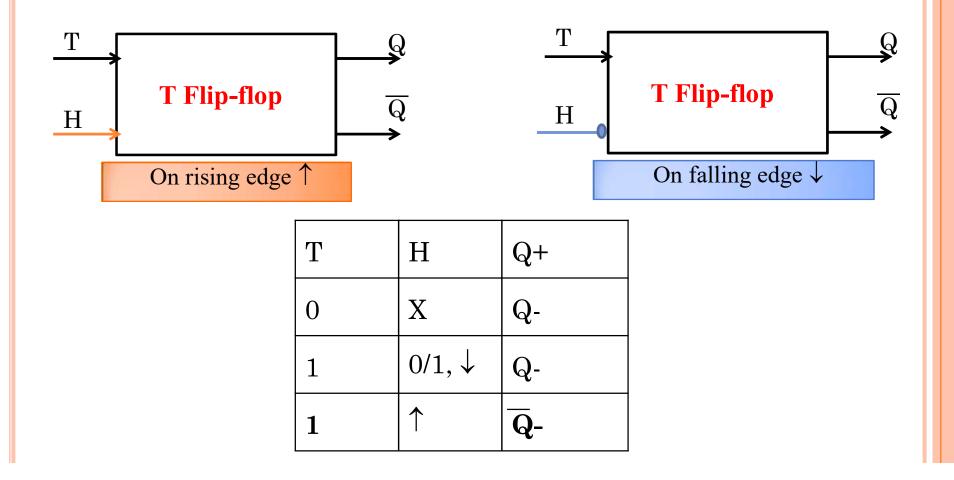

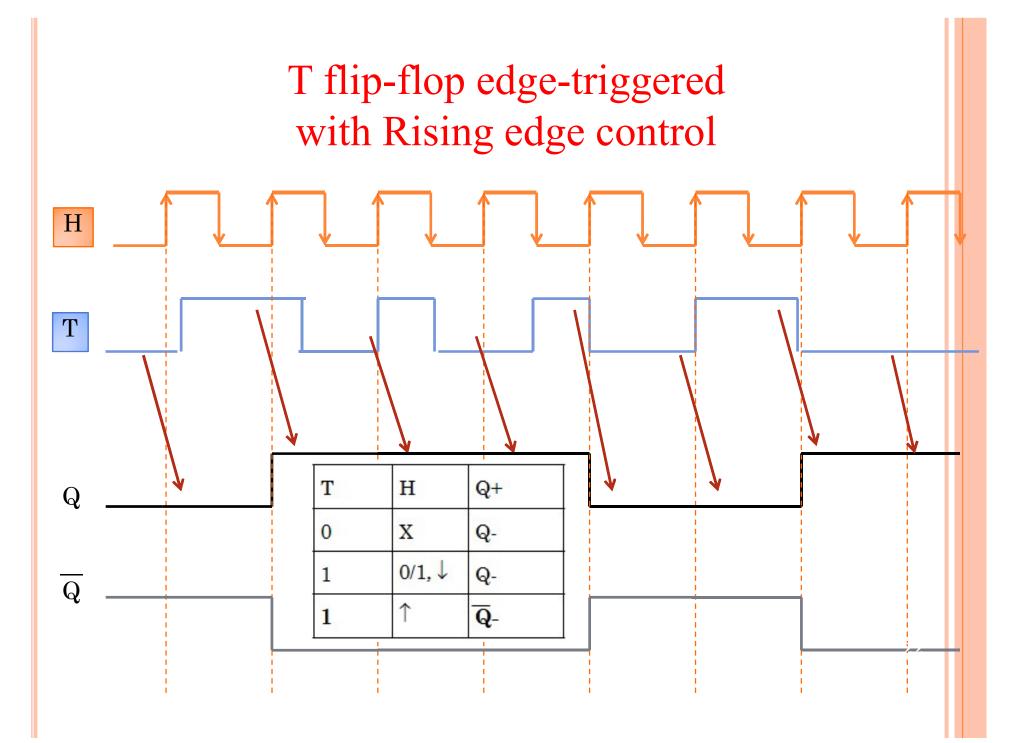

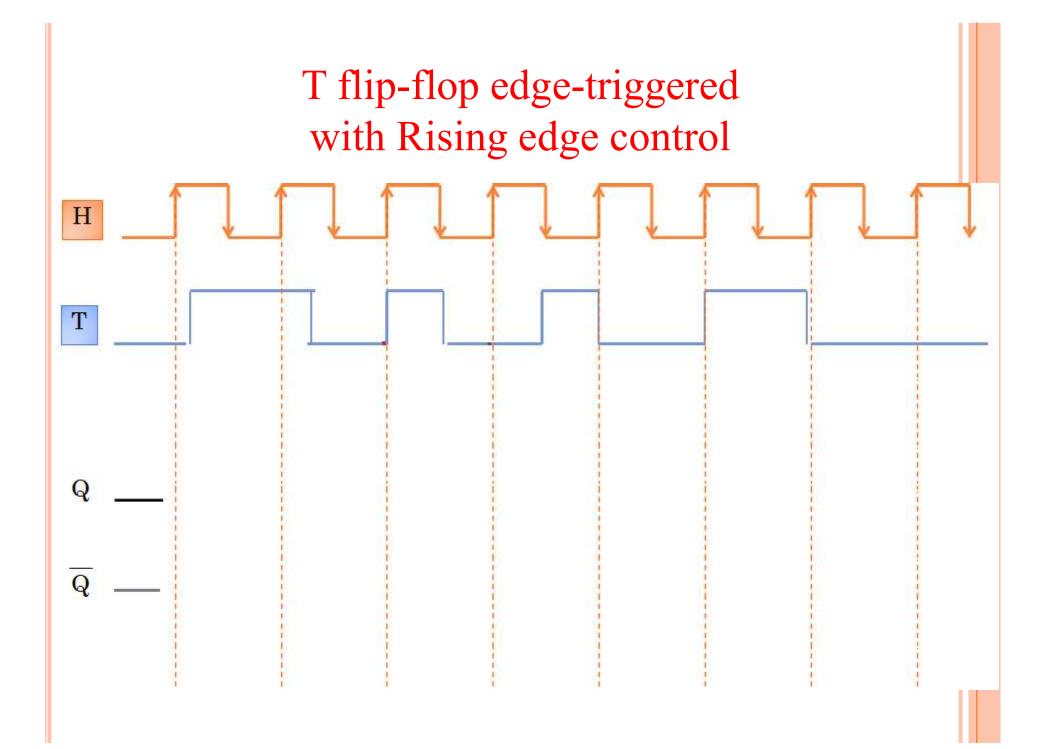

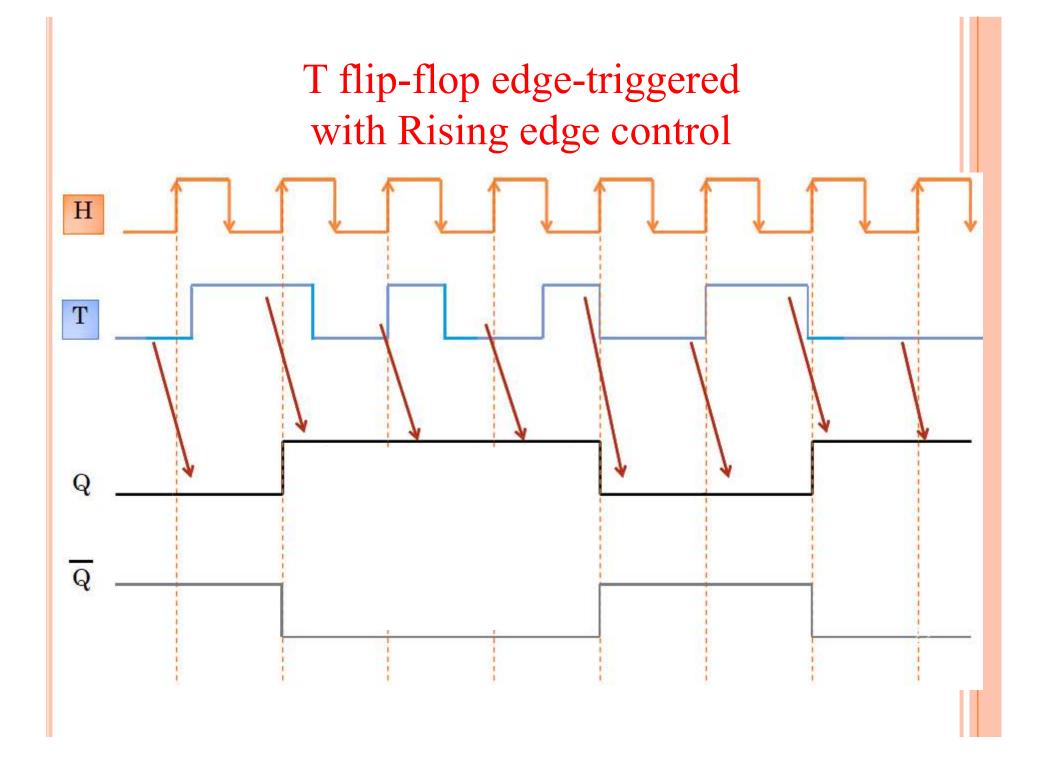

# **T** Flip-flop

The T (toggle, Trigger) flip-flop operates on a clock edge.

It allows to maintain the previous output value or to invert it (complement or not the current state). This type of flip-flop is particularly interesting for implementing counters.

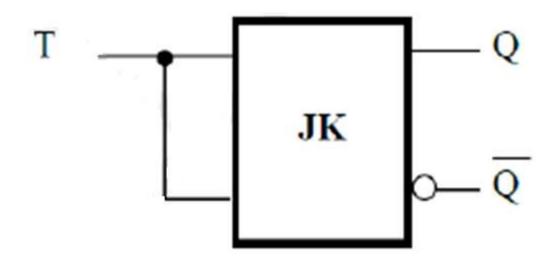

The T flip-flop can be realized from a D flip-flop.

# **T** Flip-flop

For a J-K flip-flop, we observe that if J=K=1, the state of the output is inverted at each clock cycle. Thus, the T flip-flop has a single input called 'Trigger', which can be obtained by connecting the J and K inputs to the same source. It is therefore sometimes called the complement flip-flop.

The synchronous T flip-flop is activated by the clock signal H.

The single input T (Trigger) controls the state of the flip-flop.

The output Q changes state each time the input T transitions to logic state 1 and retains its state the rest of the time.

# **T** Flip-flop

The T (Toggle) flip-flop toggles with each clock pulse (rising or falling edge) when its input T is active.

# T flip-flop

Exercise 05: Modify a D flip-flop to act as a T flip-flop (rising edge).

| Н          | Q+ |

|------------|----|

| 0/1/↓      | Q- |

| $\uparrow$ | D  |

| Т | Н     | Q+                        |

|---|-------|---------------------------|

| 0 | X     | Q-                        |

| 1 | 0/1,↓ | Q-                        |

| 1 | 1     | $\overline{\mathbf{Q}}$ - |

# JK flip-flop

Exercise 06: Convert a synchronous JK flip-flop into a D flip-flop.

| Н          | D | Q+ |

|------------|---|----|

| 0/1        | 0 | Q- |

| 0/1        | 1 | Q- |

| $\uparrow$ | 0 | 0  |

| $\uparrow$ | 1 | 1  |

| Н            | J | K | Q+ |

|--------------|---|---|----|

| 0/1          | X | X | Q- |

| $\downarrow$ | 0 | 0 | Q- |

| $\downarrow$ | 0 | 1 | 0  |

| $\downarrow$ | 1 | 0 | 1  |

| $\downarrow$ | 1 | 1 | Q- |

$$H_{JK} = \overline{H}_{D}, J = D ; K = \overline{D}$$

# JK flip-flop

Exercise 07: Transform a JK flip-flop to act as a T flip-flop (falling edge).

| Т | Н             | Q+ |

|---|---------------|----|

| 0 | X             | Q- |

| 1 | 0/1, ↑        | Q- |

| 1 | $\rightarrow$ | Q- |

| Н            | J | K | Q+ |

|--------------|---|---|----|

| 0/1, ↑       | X | X | Q- |

| $\downarrow$ | 0 | 0 | Q- |

| $\downarrow$ | 0 | 1 | 0  |

| $\downarrow$ | 1 | 0 | 1  |

| $\downarrow$ | 1 | 1 | Q- |

$$H_T = H_{JK}, J = K = T$$

#### FLIP-FLOP EXCITATION TABLE

Characteristic tables of flip-flops specify the next state when the inputs and the current state are known. However, during the design of a process (logic circuit), transition states (current state and next state) are often known, and it is the inputs that need to be determined to ensure the desired transition. For this reason, we need a table that provides the necessary inputs for a given state transition. This table is called the flip-flop (or combinational circuit) excitation table. It consists of two columns, Qt and Qt+1, and one column for each input. There are four transitions (4 rows) to go from Qt to Ot+1.

### FLIP-FLOP EXCITATION TABLE

For example, for the J-K flip-flop, to achieve the transition from 0 to 1, the J input must be in the state 1, regardless of the state of the K input.

J = K = 1 flips the state of the flip-flop, or J = 1 and K = 0 loads 1 into the flip-flop. A cross indicates that the state of the considered input is irrelevant: 0 or 1.

|   |      | RS Flip-Flop |   | D Flip-Flop | JK Flip-Flop |   | T Flip-Flop |

|---|------|--------------|---|-------------|--------------|---|-------------|

| Q | Q1+1 | s            | R | D           | J            | K | Т           |

| 0 | 0    | 0            | х | 0           | 0            | X | 0           |

| 0 | 1    | 1            | 0 | 1           | 1            | х | 1           |

| 1 | 0    | 0            | 1 | 0           | X            | 1 | 1           |

| 1 | 1    | х            | 0 | 1           | х            | 0 | 0           |

#### FLIP-FLOP INITIALIZATION

The RSH, D, T, and JK flip-flops operate synchronously with respect to a clock signal (H).

For the operation of a system, it is often necessary that these flip-flops be initialized, meaning that their output Q is set to 1 or 0 independently of the clock signal.

This is the role of two additional inputs:

- $\triangleright$  Preset: sets the output Q to 1.

- $\succ$  Clear: sets the output Q to 0.

# FLIP-FLOP INITIALIZATION

Clear (Cl) and Preset (Pr) are two asynchronous inputs that:

- $\succ$  operate with negative logic

- $\succ$  have higher priority than the clock

| Clear | Preset | Η          | Q               |

|-------|--------|------------|-----------------|

| 0     | 0      | X          | Forbidden state |

| 0     | 1      | X          | 1               |

| 1     | 0      | Х          | 0               |

| 1     | 1      | $\uparrow$ | Flip-flop       |

# FLIP-FLOP INITIALIZATION JK Flip-flop

Exercise 8: Provide the truth table of the JK flip-flop with the inputs Clear and Preset.

# Thank you for your attention