Machine Structure 02 Chapter 01-part-02 Combinatorial Circuits

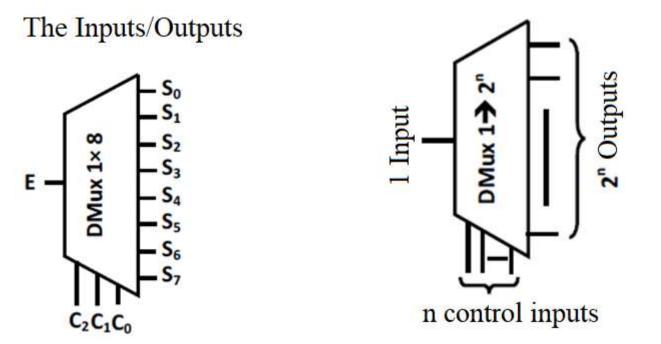

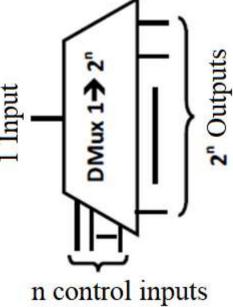

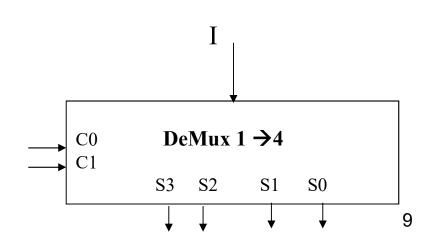

- Demultiplexer: It plays the reverse role of a multiplexer; it allows for passing information to one of the outputs based on the values of the control inputs. It has:

- <u>One</u> single input

- <u>2</u><sup>n</sup> outputs

- <u>N</u> selection inputs (controls)

- Definition: A demultiplexer is a combinational logic circuit that has a <u>1 single input</u>, <u>n control inputs</u>, and <u>2<sup>n</sup> outputs</u>, It allows routing the value of the input line to the output line indicated by its control inputs.

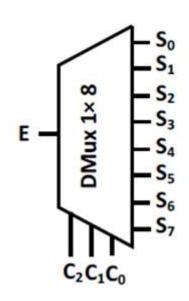

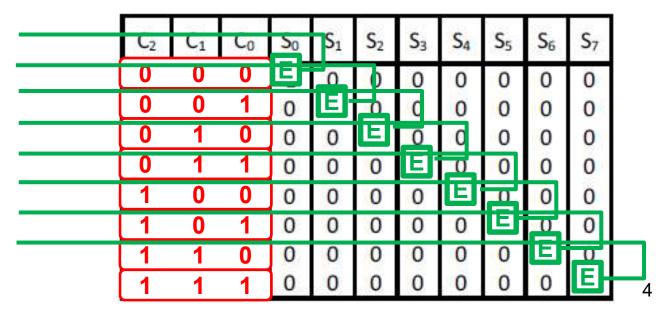

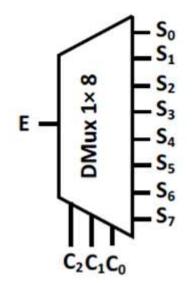

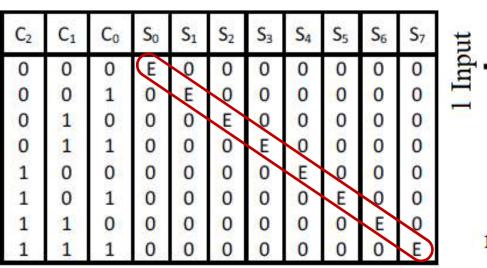

- Circuit synthesis (1x8 demultiplexer).

- Definition: A demultiplexer is a combinational logic circuit that has a <u>1 single input</u>, <u>n control inputs</u>, and <u>2<sup>n</sup> outputs</u>, It allows routing the value of the input line to the output line indicated by its control inputs.

- Circuit synthesis (1x8 demultiplexer).

The Inputs/Outputs

- Definition: A demultiplexer is a combinational logic circuit that has a <u>1 single input</u>, <u>n control inputs</u>, and <u>2<sup>n</sup> outputs</u>, It allows routing the value of the input line to the output line indicated by its control inputs.

- Circuit synthesis (1x8 demultiplexer).

The Inputs/Outputs The truth table

#### The truth table

| C <sub>2</sub> | C <sub>1</sub> | Co | S <sub>0</sub> | S1 | S <sub>2</sub> | S₃ | S <sub>4</sub> | $S_5$ | S <sub>6</sub> | <b>S</b> <sub>7</sub> |

|----------------|----------------|----|----------------|----|----------------|----|----------------|-------|----------------|-----------------------|

| 0              | 0              | 0  | Ε              | 0  | 0              | 0  | 0              | 0     | 0              | 0                     |

| 0              | 0              | 1  | 0              | Е  | 0              | 0  | 0              | 0     | 0              | 0                     |

| 0              | 1              | 0  | 0              | 0  | Е              | 0  | 0              | 0     | 0              | 0                     |

| 0              | 1              | 1  | 0              | 0  | 0              | Е  | 0              | 0     | 0              | 0                     |

| 1              | 0              | 0  | 0              | 0  | 0              | 0  | Е              | 0     | 0              | 0                     |

| 1              | 0              | 1  | 0              | 0  | 0              | 0  | 0              | Ε     | 0              | 0                     |

| 1              | 1              | 0  | 0              | 0  | 0              | 0  | 0              | 0     | E              | 0                     |

| 1              | 1              | 1  | 0              | 0  | 0              | 0  | 0              | 0     | 0              | E                     |

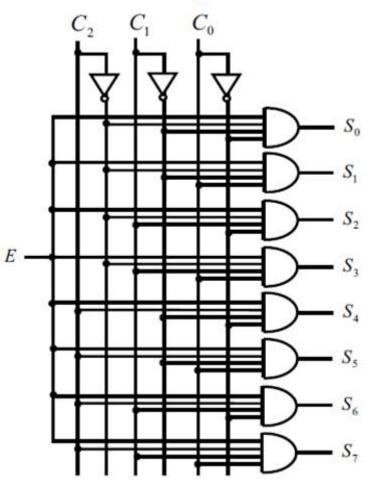

Logical Fonctions

- $S_0 = \overline{C_2} \cdot \overline{C_1} \cdot \overline{C_0} \cdot E$

- $S_1 = \overline{C_2} \cdot \overline{C_1} \cdot C_0 \cdot E$

- $S_2 = \overline{C_2} \cdot C_1 \cdot \overline{C_0} \cdot E$

- $S_3 = \overline{C_2}.C_1.C_0.E$

- $S_4 = C_2 . \overline{C_1} . \overline{C_0} . E$

- $S_5 = C_2 \cdot \overline{C_1} \cdot C_0 \cdot E$

- $S_6 = C_2.C_1.\overline{C_0}.E$

- $S_7 = C_2.C_1.C_0.E$

Logical Fonctions

- $S_0 = \overline{C_2} \cdot \overline{C_1} \cdot \overline{C_0} \cdot E$

- $S_1 = \overline{C_2} \cdot \overline{C_1} \cdot C_0 \cdot E$

- $S_2 = \overline{C_2} \cdot C_1 \cdot \overline{C_0} \cdot E$

- $S_3 = \overline{C_2} \cdot C_1 \cdot C_0 \cdot E$

- $S_4 = C_2 \cdot \overline{C_1} \cdot \overline{C_0} \cdot E$

- $S_5 = C_2 \cdot \overline{C_1} \cdot C_0 \cdot E$

- $S_6 = C_2 \cdot C_1 \cdot \overline{C_0} \cdot E$

$S_7 = C_2.C_1.C_0.E$

The circuit diagram

# Demultiplexers $1 \rightarrow 4$

Implementing a demultiplexer circuit. 1→4

### Demultiplexers $1 \rightarrow 4$

| C1 | C0 | S3 | S2 | S1 | <b>S</b> 0 |

|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 0  | i          |

| 0  | 1  | 0  | 0  | i  | 0          |

| 1  | 0  | 0  | i  | 0  | 0          |

| 1  | 1  | i  | 0  | 0  | 0          |

$S0 = \overline{C1}.\overline{C0}.(I)$  $S1 = \overline{C1}.C0.(I)$  $S2 = C1.\overline{C0}.(I)$ S3 = C1.C0.(I)

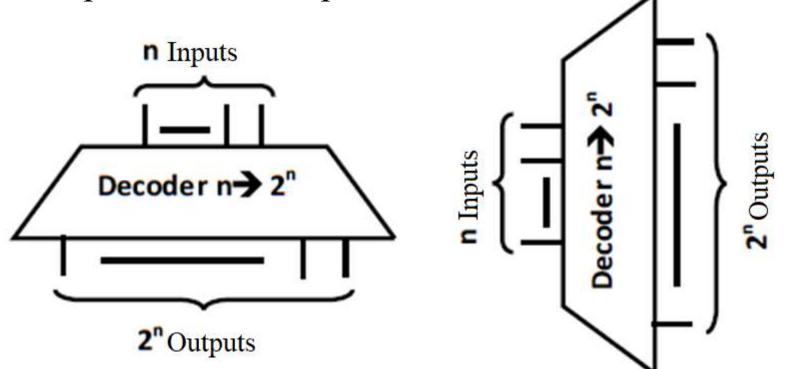

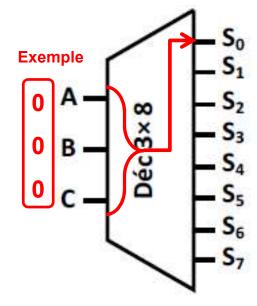

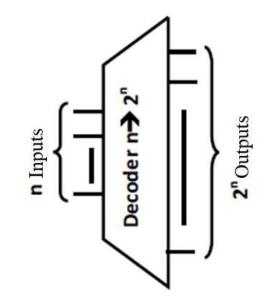

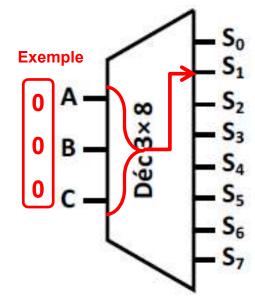

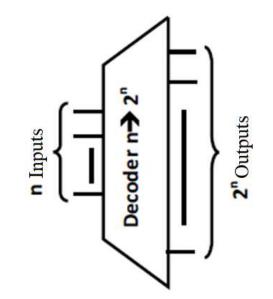

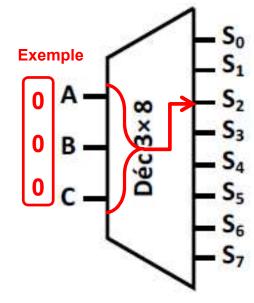

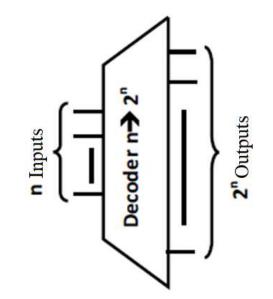

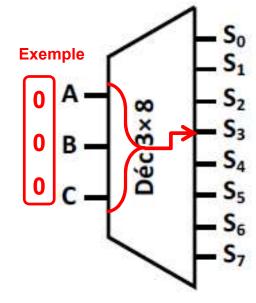

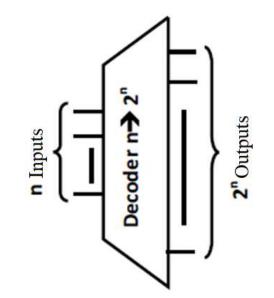

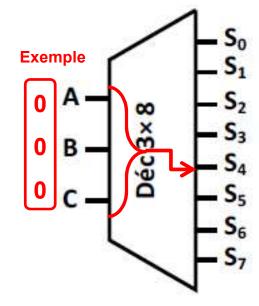

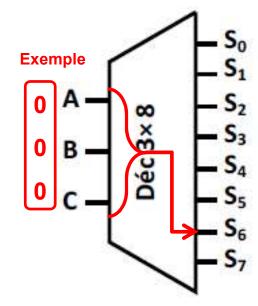

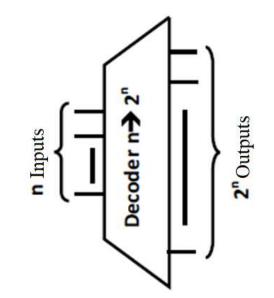

Definition: A n-bit decoder is a combinational logic circuit with  $\underline{\mathbf{n}}$  inputs and  $\underline{2^n}$  outputs. It enables the activation of the output line corresponding to the binary code present at the input.

It is a combinational circuit composed of:

- <u>N</u>: data inputs

- <u>2</u><sup>n</sup>: outputs

- For <u>each input</u> combination, <u>only one output</u> is active at a time.

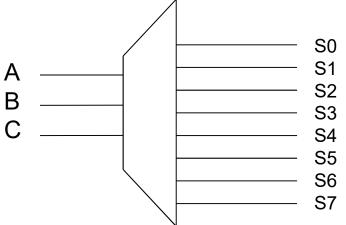

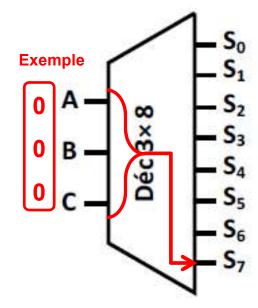

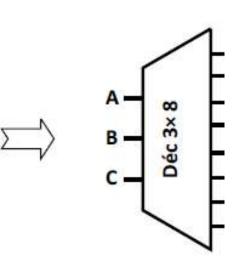

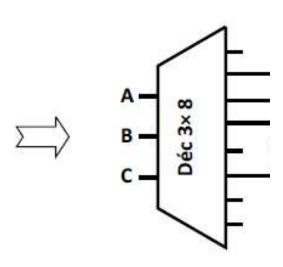

Exemple: A decoder  $3 \rightarrow 8$

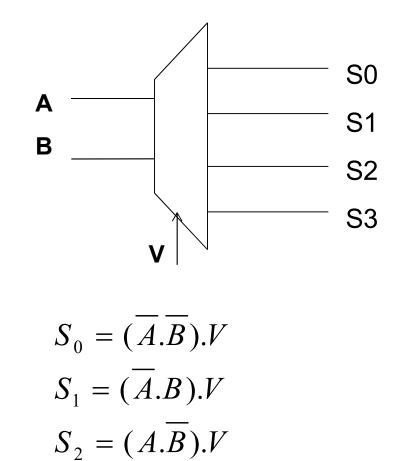

• Decoder with Enable Input Most decoders will have an enable input (EN).

This input enables the operation of the decoder.

- If  $\underline{EN} = 0$ , all outputs are set to 0.

- If  $\underline{EN} = 1$ , the decoder operates normally. We can also have: an inverted control  $\begin{array}{c} A \\ B \\ C \end{array}$

Exemple: Un decoder 3→8

S0 S1

S2

**S**3

S4 S5 S6 S7

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | В | С | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------|-------|-----------------------|

| 0 | 0 | 0 | 1              | 0              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 1 | 0              | 0              | 0              | 1              | 0              | 0                     | 0     | 0                     |

| 1 | 0 | 0 | 0              | 0              | 0              | 0              | 1              | 0                     | 0     | 0                     |

| 1 | 0 | 1 | 0              | 0              | 0              | 0              | 0              | 1                     | 0     | 0                     |

| 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 1     | 0                     |

| 1 | 1 | 1 | 0              | 0              | 0              | 0              | 0              | 0                     | 0     | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | В | С | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------|-------|-----------------------|

| 0 | 0 | 0 | 1              | 0              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 1 | 0              | 0              | 0              | 1              | 0              | 0                     | 0     | 0                     |

| 1 | 0 | 0 | 0              | 0              | 0              | 0              | 1              | 0                     | 0     | 0                     |

| 1 | 0 | 1 | 0              | 0              | 0              | 0              | 0              | 1                     | 0     | 0                     |

| 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 1     | 0                     |

| 1 | 1 | 1 | 0              | 0              | 0              | 0              | 0              | 0                     | 0     | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | в | С | S | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|---|----------------|----------------|----------------|----------------|-----------------------|-------|-----------------------|

| 0 | 0 | 0 | 1 | 0              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 0 | 1 | 0 | 1              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 0 | 0 | 0              | 1              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 1 | 0 | 0              | 0              | 1              | 0              | 0                     | 0     | 0                     |

| 1 | 0 | 0 | 0 | 0              | 0              | 0              | 1              | 0                     | 0     | 0                     |

| 1 | 0 | 1 | 0 | 0              | 0              | 0              | 0              | 1                     | 0     | 0                     |

| 1 | 1 | 0 | 0 | 0              | 0              | 0              | 0              | 0                     | 1     | 0                     |

| 1 | 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0                     | 0     | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | в | С | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------|-------|-----------------------|

| 0 | 0 | 0 | 1              | 0              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 1 | 0              | 0              | 0              | 1              | 0              | 0                     | 0     | 0                     |

| 1 | 0 | 0 | 0              | 0              | 0              | 0              | 1              | 0                     | 0     | 0                     |

| 1 | 0 | 1 | 0              | 0              | 0              | 0              | 0              | 1                     | 0     | 0                     |

| 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 1     | 0                     |

| 1 | 1 | 1 | 0              | 0              | 0              | 0              | 0              | 0                     | 0     | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | в | с | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------|-------|-----------------------|

| 0 | 0 | 0 | 1              | 0              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 1 | 0              | 0              | 0              | 1              | 0              | 0                     | 0     | 0                     |

| 1 | 0 | 0 | 0              | 0              | 0              | 0              | 1              | 0                     | 0     | 0                     |

| 1 | 0 | 1 | 0              | 0              | 0              | 0              | 0              | 1                     | 0     | 0                     |

| 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 1     | 0                     |

| 1 | 1 | 1 | 0              | 0              | 0              | 0              | 0              | 0                     | 0     | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | в | С | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|-----------------------|

| 0 | 0 | 0 | 1              | 0              | 0              | 0              | 0              | 0                     | 0              | 0                     |

| 0 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0                     | 0              | 0                     |

| 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 0                     | 0              | 0                     |

| 0 | 1 | 1 | 0              | 0              | 0              | 1              | 0              | 0                     | 0              | 0                     |

| 1 | 0 | 0 | 0              | 0              | 0              | 0              | 1              | 0                     | 0              | 0                     |

| 1 | 0 | 1 | 0              | 0              | 0              | 0              | 0              | 1                     | 0              | 0                     |

| 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0              | 0                     | 1              | 0                     |

| 1 | 1 | 1 | 0              | 0              | 0              | 0              | 0              | 0                     | 0              | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | В | С | S <sub>0</sub> | <b>S</b> <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|-----------------------|----------------|----------------|----------------|-----------------------|-------|-----------------------|

| 0 | 0 | 0 | 1              | 0                     | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 0 | 1 | 0              | 1                     | 0              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 0 | 0              | 0                     | 1              | 0              | 0              | 0                     | 0     | 0                     |

| 0 | 1 | 1 | 0              | 0                     | 0              | 1              | 0              | 0                     | 0     | 0                     |

| 1 | 0 | 0 | 0              | 0                     | 0              | 0              | 1              | 0                     | 0     | 0                     |

| 1 | 0 | 1 | 0              | 0                     | 0              | 0              | 0              | 1                     | 0     | 0                     |

| 1 | 1 | 0 | 0              | 0                     | 0              | 0              | 0              | 0                     | 1     | 0                     |

| 1 | 1 | 1 | 0              | 0                     | 0              | 0              | 0              | 0                     | 0     | 1                     |

Circuit synthesis (3x8 decoder). The Inputs/Outputs

| Α | в | С | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|----------------|-------|-----------------------|

| 0 | 0 | 0 | 1              | 0              | 0              | 0              | 0              | 0              | 0     | 0                     |

| 0 | 0 | 1 | 0              | 1              | 0              | 0              | 0              | 0              | 0     | 0                     |

| 0 | 1 | 0 | 0              | 0              | 1              | 0              | 0              | 0              | 0     | 0                     |

| 0 | 1 | 1 | 0              | 0              | 0              | 1              | 0              | 0              | 0     | 0                     |

| 1 | 0 | 0 | 0              | 0              | 0              | 0              | 1              | 0              | 0     | 0                     |

| 1 | 0 | 1 | 0              | 0              | 0              | 0              | 0              | 1              | 0     | 0                     |

| 1 | 1 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | 1     | 0                     |

| 1 | 1 | 1 | 0              | 0              | 0              | 0              | 0              | 0              | 0     | 1                     |

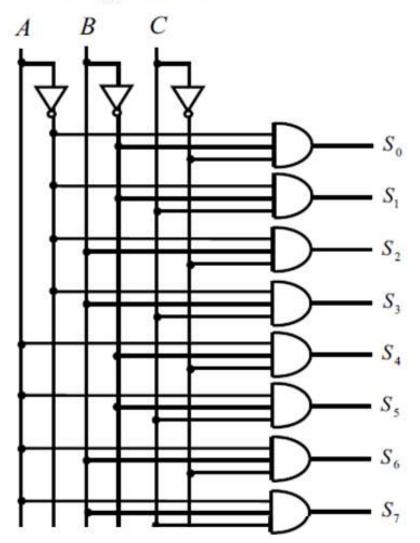

#### Circuit synthesis (3x8 decoder).

#### The truth table

Logical expression

$S_0 = \overline{A} \cdot \overline{B} \cdot \overline{C}$

$$S_1 = \overline{A} \cdot \overline{B} \cdot C$$

$$S_2 = \overline{A} \cdot B \cdot \overline{C}$$

$$S_3 = \overline{A} \cdot B \cdot C$$

$$S_4 = A \cdot \overline{B} \cdot \overline{C}$$

$$S_5 = A \cdot \overline{B} \cdot C$$

$$S_6 = A . B. \overline{C}$$

$$S_7 = A \cdot B \cdot C$$

Logical expression  $S_0 = \overline{A} \cdot \overline{B} \cdot \overline{C}$  $S_1 = \overline{A} \cdot \overline{B} \cdot C$  $S_2 = \overline{A} \cdot B \cdot \overline{C}$  $S_3 = \overline{A} \cdot B \cdot C$  $S_4 = A \cdot \overline{B} \cdot \overline{C}$  $S_5 = A \cdot \overline{B} \cdot C$  $S_6 = A \cdot B \cdot \overline{C}$  $S_7 = A \cdot B \cdot C$

The diagram circuit.

22

#### $2 \rightarrow 4$ decoder with enable signal.

| V | A | В | S0 | S1 | S2 | S3 |

|---|---|---|----|----|----|----|

| 0 | X | X | 0  | 0  | 0  | 0  |

| 1 | 0 | 0 | 1  | 0  | 0  | 0  |

| 1 | 0 | 1 | 0  | 1  | 0  | 0  |

| 1 | 1 | 0 | 0  | 0  | 1  | 0  |

| 1 | 1 | 1 | 0  | 0  | 0  | 1  |

$S_{3} = (A.B).V$

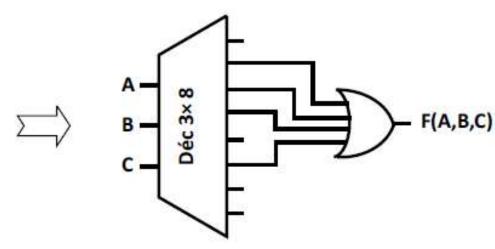

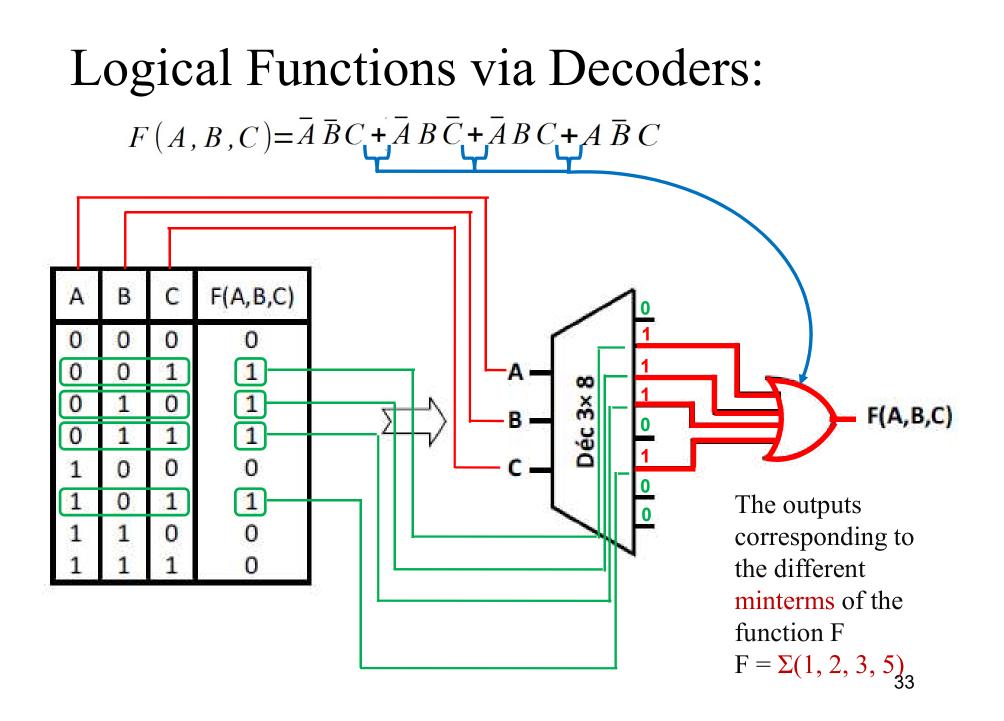

• It is also possible to generate arbitrary logical functions using decoders and basic logic gates. Simply connect the <u>variables of the function</u> to be generated to the <u>inputs</u> of the decoder and connect the <u>outputs</u> corresponding to the different <u>minterms</u> of the function to the inputs of one or more basic logic gates.

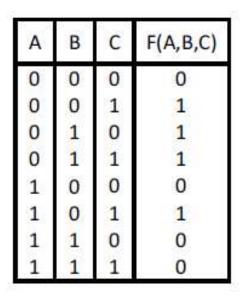

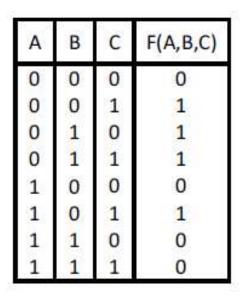

- •Example 1:

- •Implement the function:  $F(A, B, C) = \overline{B}C + \overline{A}B$

- •using an 8x1 decoder.

**Example 1:** Implement  $F(A, B, C) = \overline{B}C + \overline{A}B$ the function using an 8x1 decoder.

$F(A, B, C) = \overline{B}C + \overline{A}B$

$$F(A, B, C) = \overline{B}C + \overline{A}B$$

$$F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$$

$$F(A, B, C) = BC + \overline{A}B$$

$$F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$$

$$F(A, B, C) = (\overline{A}\overline{B}C + A\overline{B}C) + (\overline{A}B\overline{C} + \overline{A}BC)$$

**Example 1:** Implement  $F(A, B, C) = \overline{B}C + \overline{A}B$ the function using an 8x1 decoder.

$F(A, B, C) = \overline{B}C + \overline{A}B$   $F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$   $F(A, B, C) = (\overline{A}\overline{B}C + A\overline{B}C) + (\overline{A}B\overline{C} + \overline{A}BC)$   $F(A, B, C) = \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}BC + A\overline{B}C$

$$F(A, B, C) = \overline{B}C + \overline{A}B$$

$$F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$$

$$F(A, B, C) = (\overline{A}\overline{B}C + A\overline{B}C) + (\overline{A}B\overline{C} + \overline{A}BC)$$

$$F(A, B, C) = \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}BC + A\overline{B}C$$

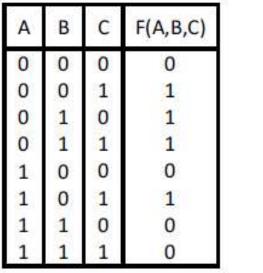

| Α | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 0        |

| 1 | 1 | 1 | 0        |

$$F(A, B, C) = \overline{B}C + \overline{A}B$$

$$F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$$

$$F(A, B, C) = (\overline{A}\overline{B}C + A\overline{B}C) + (\overline{A}B\overline{C} + \overline{A}BC)$$

$$F(A, B, C) = \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}BC + A\overline{B}C$$

$$F(A, B, C) = \overline{B}C + \overline{A}B$$

$$F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$$

$$F(A, B, C) = (\overline{A}\overline{B}C + A\overline{B}C) + (\overline{A}B\overline{C} + \overline{A}BC)$$

$$F(A, B, C) = \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}BC + A\overline{B}C$$

$$F(A, B, C) = \overline{B}C + \overline{A}B$$

$$F(A, B, C) = \overline{B}C(A + \overline{A}) + \overline{A}B(C + \overline{C})$$

$$F(A, B, C) = (\overline{A}\overline{B}C + A\overline{B}C) + (\overline{A}B\overline{C} + \overline{A}BC)$$

$$F(A, B, C) = \overline{A}\overline{B}C + \overline{A}B\overline{C} + \overline{A}BC + A\overline{B}C$$

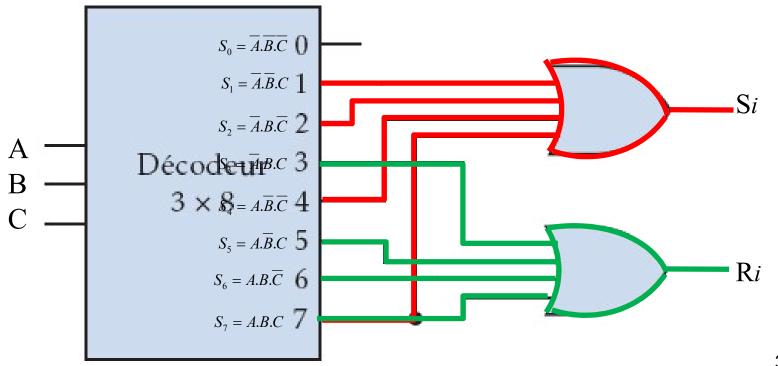

# Implementation of a <u>full adder</u> with $3 \rightarrow 8$ <u>binary decoders</u>.

• Reminder:

Truth table of a full adder for 1 bit.

| A <sub>i</sub> | B <sub>i</sub> | R <sub>i-1</sub> | <b>R</b> <sub>i</sub> | S <sub>i</sub> |

|----------------|----------------|------------------|-----------------------|----------------|

| 0              | 0              | 0                | 0                     | 0              |

| 0              | 0              | 1                | 0                     | 1              |

| 0              | 1              | 0                | 0                     | 1              |

| 0              | 1              | 1                | 1                     | 0              |

| 1              | 0              | 0                | 0                     | 1              |

| 1              | 0              | 1                | 1                     | 0              |

| 1              | 1              | 0                | 1                     | 0              |

| 1              | 1              | 1                | 1                     | 1              |

| 0 + 0 = 0       | Carry 0 |

|-----------------|---------|

| 0+1 = 1 + 0 = 1 | Carry 0 |

| 1 + 1 = 0       | Carry 1 |

| 1+1+1 = 1       | Carry 1 |

Implementation of a <u>full adder</u> with  $3 \rightarrow 8$  <u>binary decoders</u>.

$$S_{i} = \overline{A}_{i} \cdot \overline{B}_{i} \cdot R_{i-1} + \overline{A}_{i} \cdot B_{i} \cdot \overline{R}_{i-1} + A_{i} \cdot \overline{B}_{i} \cdot \overline{R}_{i-1} + A_{i} \cdot B_{i} \cdot R_{i-1}$$

**0 0 1 0 1 0 1 0 0 1 1 1**

$$R_{i} = \overline{A}_{i} B_{i} R_{i-1} + A_{i} \overline{B}_{i} R_{i-1} + A_{i} B_{i} \overline{R}_{i-1} + A_{i} B_{i} R_{i-1}$$

| A <sub>i</sub> | B <sub>i</sub> | R <sub>i-1</sub> | R <sub>i</sub> | S <sub>i</sub> |

|----------------|----------------|------------------|----------------|----------------|

| 0              | 0              | 0                | 0              | 0              |

| 0              | 0              | 1                | 0              | 1              |

| 0              | 1              | 0                | 0              | 1              |

| 0              | 1              | 1                | 1              | 0              |

| 1              | 0              | 0                | 0              | 1              |

| 1              | 0              | 1                | 1              | 0              |

| 1              | 1              | 0                | 1              | 0              |

| 1              | 1              | 1                | 1              | 1              |

# Implementation of a <u>full adder</u> with $3 \rightarrow 8$ <u>binary decoders</u>.

We suppose  $A=A_i$ ,  $B=B_i$ ,  $C=R_{i-1}C$ Then:

$$S_0 = \overline{A}.\overline{B}.\overline{C},$$

$S_1 = \overline{A}.\overline{B}.C,$   $S_2 = \overline{A}.B.\overline{C},$   $S_3 = \overline{A}.B.C,$

$S_4 = \overline{A}.\overline{B}.\overline{C},$   $S_5 = \overline{A}.\overline{B}.C,$   $S_6 = \overline{A}.B.\overline{C},$   $S_7 = \overline{A}.B.C$

$$R_{i} = S3 + S5 + S6 + S7$$

$$S_{i} = S1 + S2 + S4 + S7$$

#### Implementation of a <u>full adder</u> with $3 \rightarrow 8$ <u>binary decoders</u>. We suppose A=A<sub>i</sub>, B=B<sub>i</sub>, C=R<sub>i-1</sub>C Then: $S_i = S1 + S2 + S4 + S7$ $R_i = S3 + S5 + S6 + S7$

37

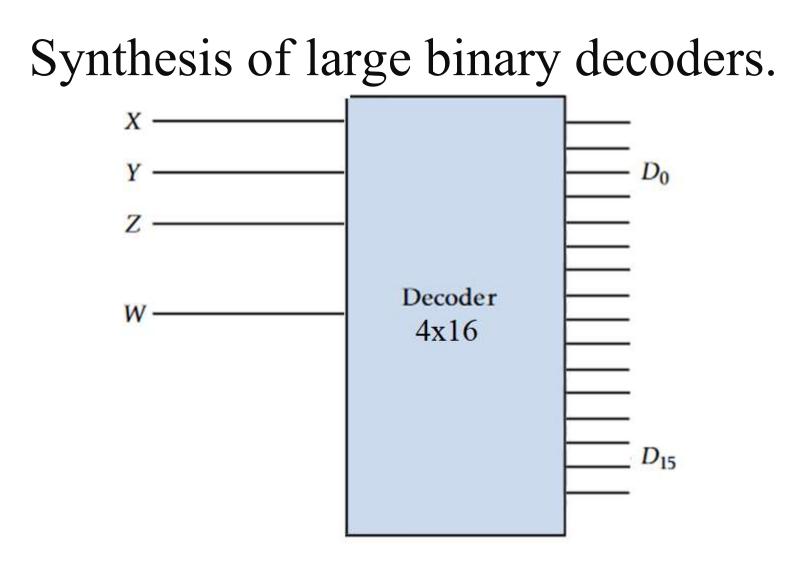

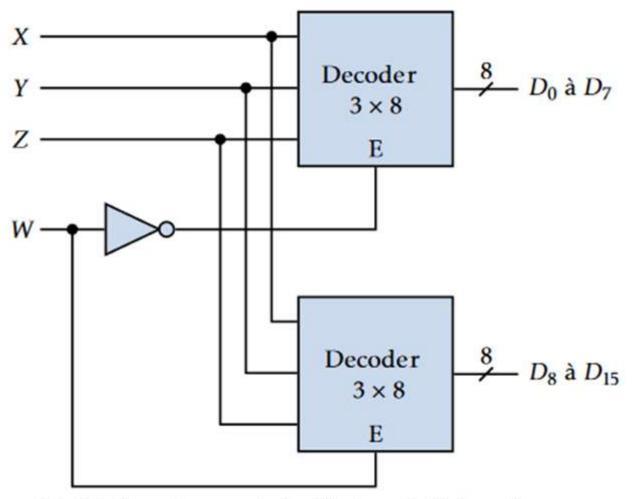

# Synthesis of large binary decoders. Example: $3 \rightarrow 8$

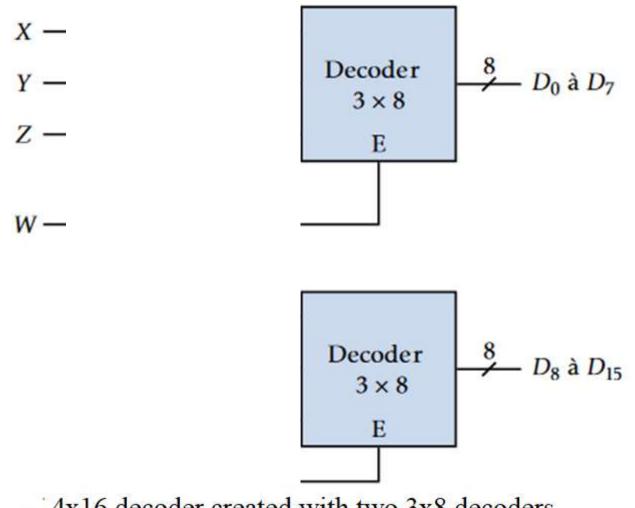

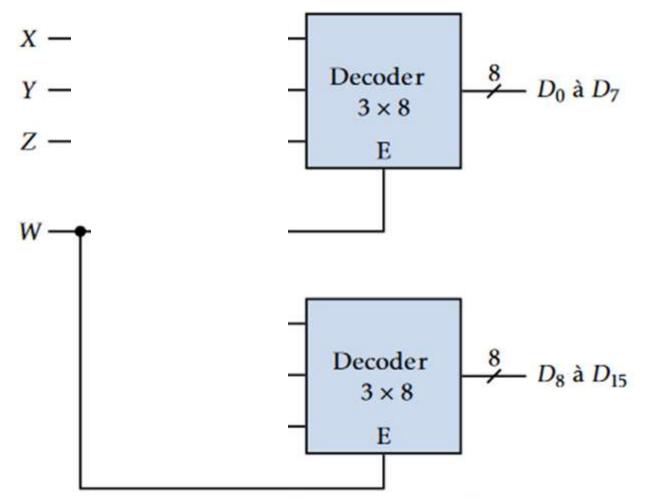

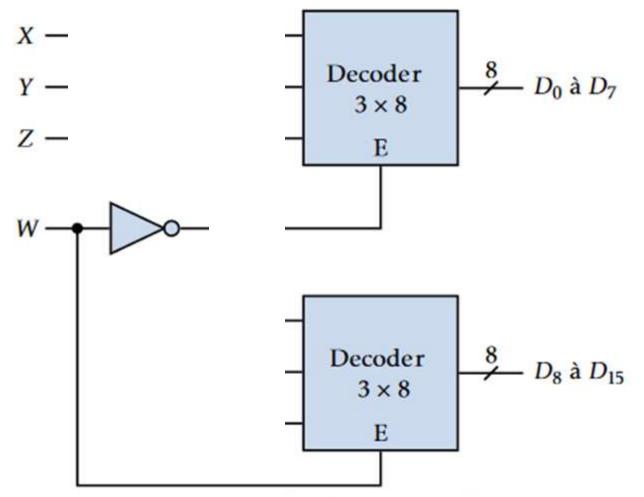

- Using 2 decoders  $3 \times 8$  to create a  $4 \times 16$  decoder.

- Decoders with <u>enable inputs</u> can be combined to create larger decoders.

- For example, we can use 2 decoders 3 × 8 to create a 4 × 16 decoder.

- The fourth variable is used to activate one or the other of the  $3 \times 8$  decoders.

- In the following figure: The input W activates only one of the two decoders at a time.

- 4x16 decoder

### Synthesis of large binary decoders.

Synthesis of large binary decoders.

Synthesis of large binary decoders.

Synthesis of large binary decoders.

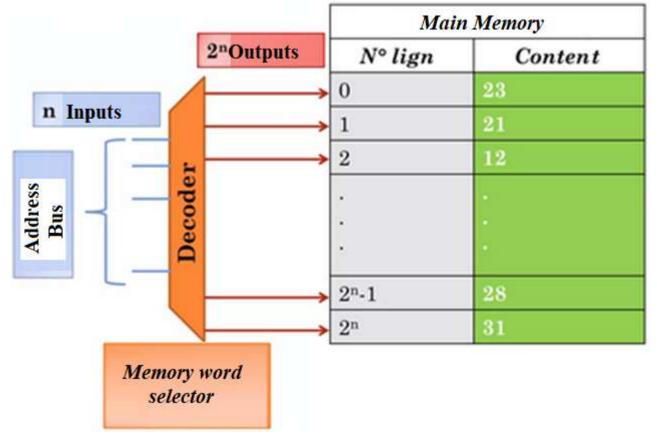

### Example of decoder application

• The decoder is an essential component at the input of the main memory.

### Example of decoder application

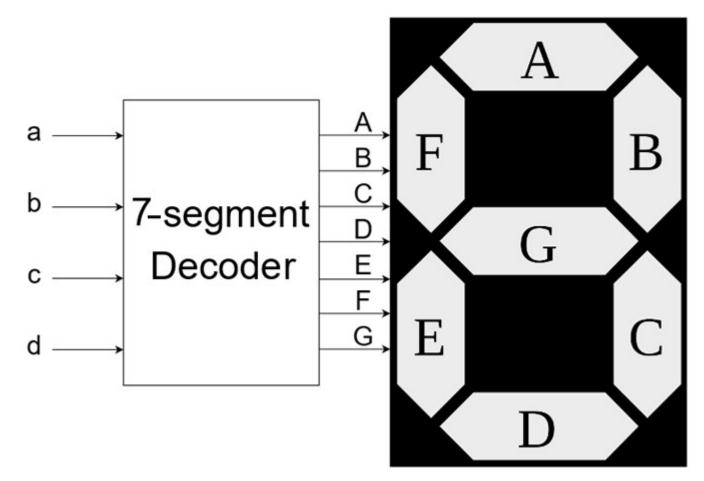

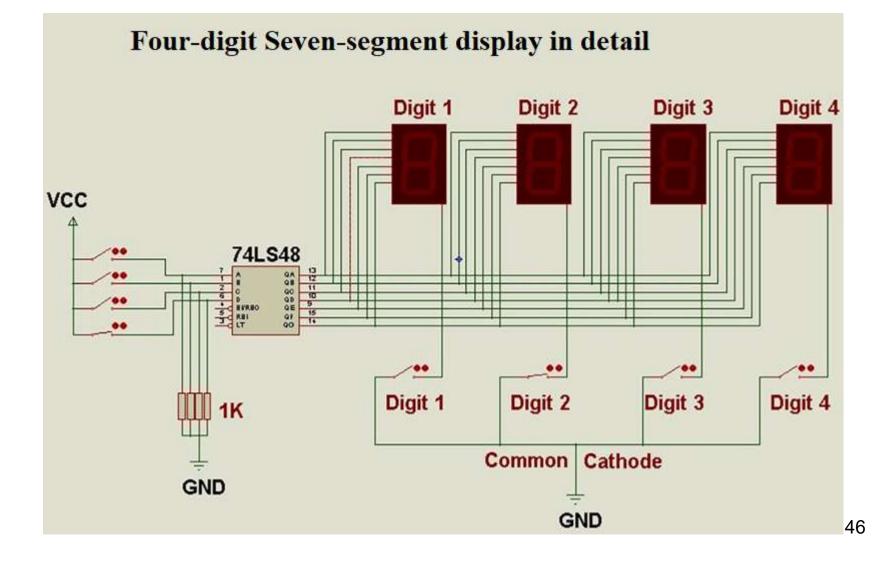

• Seven-segment display:

### Example of decoder application

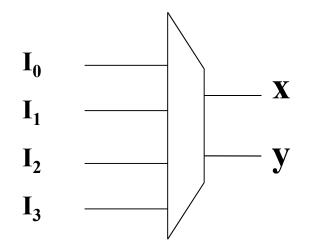

- It plays the opposite role of a decoder. It has :  $I_1$

- **Example: Encoder 4** $\rightarrow$ **2** $I_2$  $I_3$ •  $2^n$  inputs.

- N output.

- For each input combination, its number (in binary) will appear at the output.

- A coder generates the binary code equivalent to the numbers of an activated input.

- A coder detects which is the active input among 2<sup>n</sup> of n standard inputs.

I<sub>0</sub> —

Х

- For example, if input I<sub>2</sub> is active, it generates the output code 10.

- It is a device that performs the operation of a decoder: <u>only one input among M is activated at a time</u>, which corresponds to a binary number at the output.

- A priority encoder, if two inputs are active simultaneously, prioritizes one.

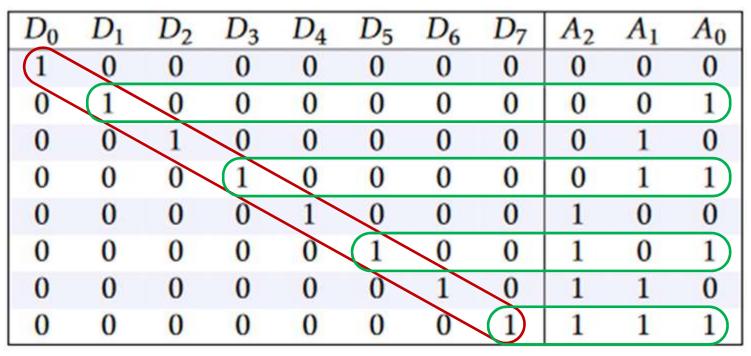

• Example: The truth table of an 8-to-3 encoder is shown in the following figure:

The truth table of Encoder  $8 \rightarrow 3$

- Exemple:

- The truth table of an 8-to-3 encoder is shown in the following figure: The outputs are obtained with OR gates,

- For example, output A₀ = 1

When inputs 1, 3, 5, or 7 are 1. We then obtain the following equations:

$$A_0 = D_1 + D_3 + D_5 + D_7$$

- $A_1 = D_2 + D_3 + D_6 + D_7$

- $A_2 = D_4 + D_5 + D_6 + D_7$

- So, the 8-to-3 encoder can be implemented with three 3-input OR gates.

- <u>Note:</u> Only one input must be activated at a time, otherwise, there will be an error.

- For example, If we <u>simultaneously</u> activate inputs  $D_3$ and  $D_6$ , so  $D_3 = D_6 = 1$ , the output will be:

$A_2 = 1$ ,  $A_1 = 1$  et  $A_0 = 1$ , which would mean that input 7 is activated.

$$A_0 = D_1 + D_3 + D_5 + D_7$$

$$A_1 = D_2 + D_3 + D_6 + D_7$$

$$A_2 = D_4 + D_5 + D_6 + D_7$$

The truth table of this encoder is shown in the following figure:

The truth table of Encoder  $8 \rightarrow 3$

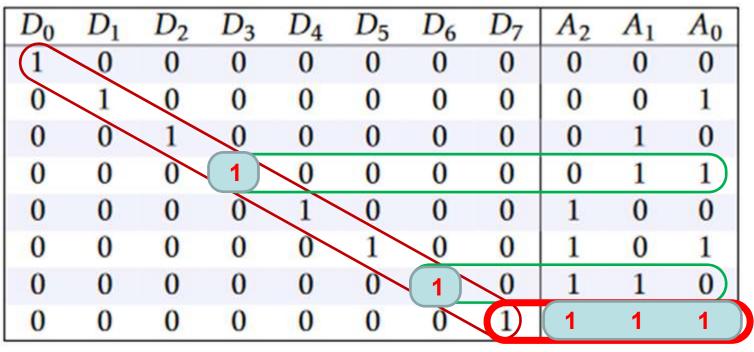

- To address this issue, we modify the encoder so that the highest input has priority: **<u>it's a priority encoder</u>**.

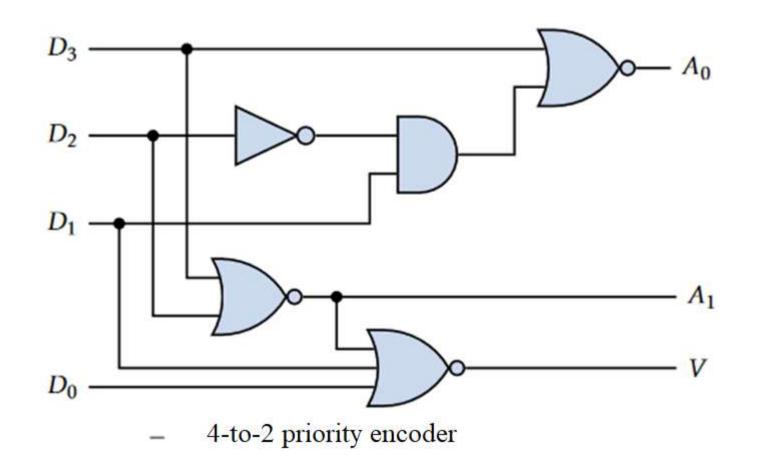

- Example 2: The truth table of a 4-to-2 encoder is shown in the figure. Note the use of don't-care conditions. We also have a validation output: V = 1 if any of the inputs are 1, otherwise V = 0. The circuit is shown in the figure.  $D_0 \quad D_1 \quad D_2 \quad D_3 \quad A_1 \quad A_0 \quad V$

| $D_0$ | $D_1$ | $D_2$ | $D_3$ | $A_1$ | $A_0$ | V |

|-------|-------|-------|-------|-------|-------|---|

| 0     | 0     | 0     | 0     | X     | X     | 0 |

| 1     | 0     | 0     | 0     | 0     | 0     | 1 |

| Х     | 1     | 0     | 0     | 0     | 1     | 1 |

| X     | Х     | 1     | 0     | 1     | 0     | 1 |

| Х     | X     | Х     | 1     | 1     | 1     | 1 |

• The circuit is shown in the figure.

# Binairy Encoder $4 \rightarrow 2$

| I <sub>0</sub> | I <sub>1</sub> | <b>I</b> <sub>2</sub> | 3 | X | У |

|----------------|----------------|-----------------------|---|---|---|

| 0              | 0              | 0                     | 0 | 0 | 0 |

| 1              | X              | x                     | X | 0 | 0 |

| 0              | 1              | x                     | X | 0 | 1 |

| 0              | 0              | 1                     | X | 1 | 0 |

| 0              | 0              | 0                     | 1 | 1 | 1 |

$$X = \overline{I0}.\overline{I1}.(I2 + I3)$$

$$Y = \overline{I0}.(I1 + .\overline{I2}.I3)$$

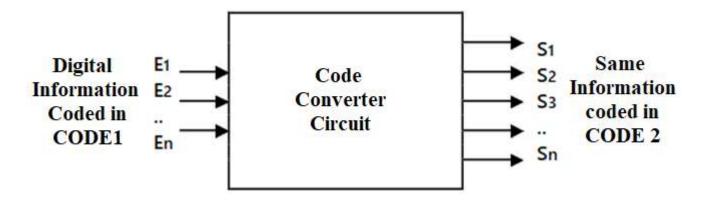

# Transcoder

- Combinational transcode circuits (also known as code converters) fall into 3 categories:

- Encoders,

- Decoders,

- Transcoders.

- All these logic circuits transform information present at their inputs in one format (code 1) into the same information present at their outputs in a different format (code 2).

### Transcoder

- We call:

- Encoder: a circuit with  $2^{n}$  inputs and <u>n</u> outputs.

- Decoder: a circuit with <u>n</u> inputs and <u>2</u><sup>n</sup> outputs, where only one is activated at a time.

- Transcoder: any other code converter circuit different from the previous ones, with  $\underline{P}$  inputs and  $\underline{K}$  outputs.

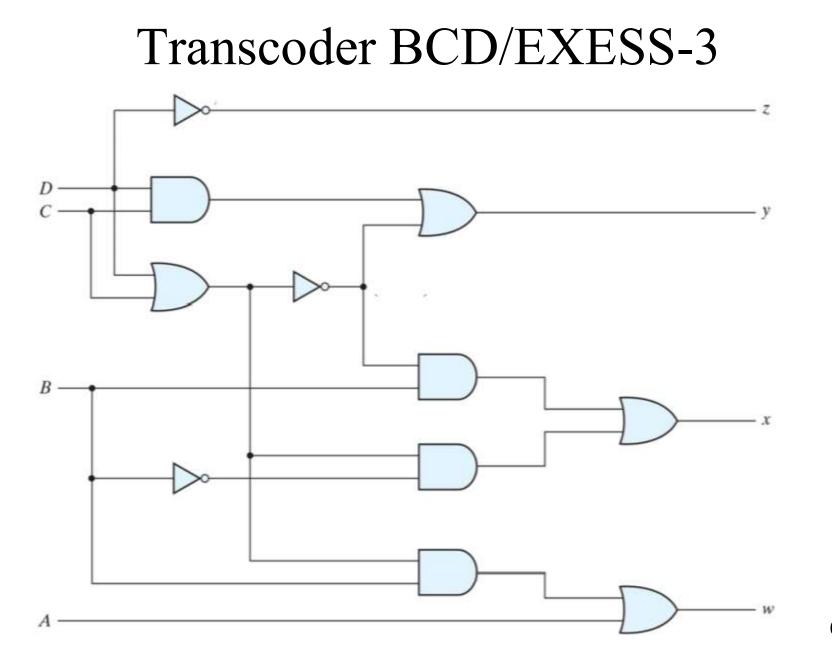

#### Example:

The implementation of a transcoder:

We want to perform a transcoding from BCD code to Excess-3 code.

The input and output numbers are expressed in 4 bits, and this transcoder will be able to convert all digits from 0 to 9.

Solution: Step -1 in designing the transcoder: Writing the truth table:

|                |    | Entrées (BCD) |    |    |    | Sorties (XS 3) |                |  |  |

|----------------|----|---------------|----|----|----|----------------|----------------|--|--|

| E <sub>3</sub> | E2 | E1            | E₀ | S₃ | S2 | S1             | S <sub>0</sub> |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

|                |    |               |    |    |    |                |                |  |  |

- Step 2 in designing the transcoder: Searching for and simplifying the equations of the outputs: S0=...., S1=...., S2=...., S3=....

- Step 3 in designing the transcoder: Drawing the logic diagram.

- Note: among the 16 possible combinations applicable to the 4 inputs of the transcoder, only 10 combinations will be used (to encode the 10 digits to be converted). The other 6 will never be present at the input of the transcoder. Crosses then appear in 6 cells of the Karnaugh maps of the outputs, which allows for a significant simplification of the logic equations.

| Α | В | С | D | X | Υ | Ζ | Τ |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | x | x | x | x |

| 1 | 0 | 1 | 1 | x | x | x | x |

| 1 | 1 | 0 | 0 | x | x | x | x |

| 1 | 1 | 0 | 1 | x | x | x | x |

| 1 | 1 | 1 | 0 | x | x | x | x |

| 1 | 1 | 1 | 1 | X | x | x | X |

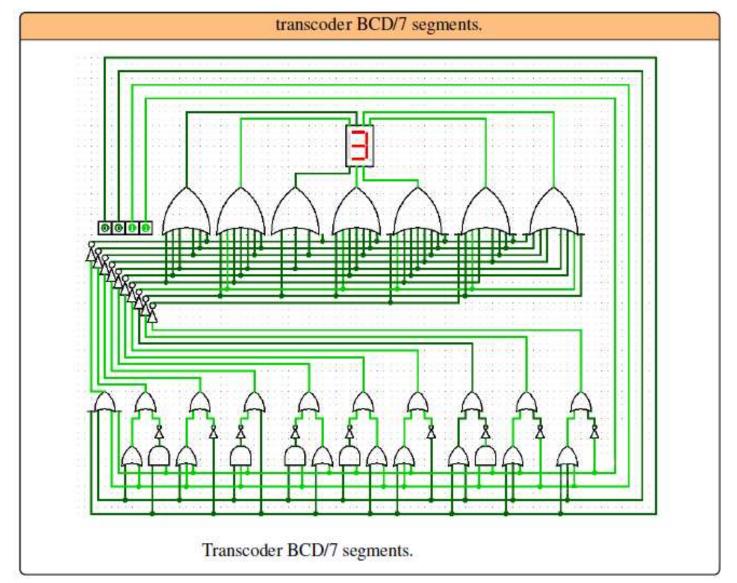

#### Transcoder BCD/7 segments

63

- <u>Note:</u> Among the transcoders found in integrated circuits:

- Decimal / BCD transcoders (74147 circuit)

- BCD / Decimal transcoders (7442, 7445, and 4028 circuits)

- XS 3 / Decimal transcoders (7443 circuit)

- Excess-3 Gray transcoders (Gray+3) / Decimal (7444 circuit)

- DCB / 7-segment display transcoders (7448, 7511, 4543, 4511 circuits)

- 5-bit binary / DCB transcoders (74185 circuit)

- DCB / 5-bit binary transcoders (74184 circuit)